#### 저작자표시-비영리-변경금지 2.0 대한민국

#### 이용자는 아래의 조건을 따르는 경우에 한하여 자유롭게

• 이 저작물을 복제, 배포, 전송, 전시, 공연 및 방송할 수 있습니다.

#### 다음과 같은 조건을 따라야 합니다:

저작자표시. 귀하는 원저작자를 표시하여야 합니다.

비영리. 귀하는 이 저작물을 영리 목적으로 이용할 수 없습니다.

변경금지. 귀하는 이 저작물을 개작, 변형 또는 가공할 수 없습니다.

- 귀하는, 이 저작물의 재이용이나 배포의 경우, 이 저작물에 적용된 이용허락조건 을 명확하게 나타내어야 합니다.

- 저작권자로부터 별도의 허가를 받으면 이러한 조건들은 적용되지 않습니다.

저작권법에 따른 이용자의 권리는 위의 내용에 의하여 영향을 받지 않습니다.

이것은 이용허락규약(Legal Code)을 이해하기 쉽게 요약한 것입니다.

# Ph. D. Thesis 박사 학위논문

# Ultra-low Power Receivers Based on Injection Locked Oscillators

Soonyoung Hong (홍 순 영 洪 淳 英)

Department of

Information and Communication Engineering

**DGIST**

2021

# Ph. D. Thesis 박사 학위논문

# Ultra-low Power Receiver Based on Injection Locked Oscillators

Soonyoung Hong (홍 순 영 洪 淳 英)

Department of

Information and Communication Engineering

**DGIST**

2021

# Ultra-low Power Receiver Based on Injection Locked Oscillators

Advisor: Professor Junghyup Lee Co-advisor: Professor Minkyu Je

by

Soonyoung Hong

Department of Information and Communication Engineering

DGIST

A thesis submitted to the faculty of DGIST in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Department of Information and Communication Engineering. The study was conducted in accordance with Code of Research Ethics<sup>1</sup>

11.06.2020

Approved by

Professor Junghyup Lee (signature)

(Advisor)

Professor Minkyu Je (signature)

(Co-Advisor)

<sup>1</sup> Declaration of Ethical Conduct in Research: I, as a graduate student of DGIST, hereby declare that I have not committed any acts that may damage the credibility of my research. These include, but are not limited to: falsification, thesis written by someone else, distortion of research findings or plagiarism. I affirm that my thesis contains honest conclusions based on my own careful research under the guidance of my thesis advisor.

# Ultra-low Power Receiver Based on Injection Locked Oscillators

## Soonyoung Hong

Accepted in partial fulfillment of the requirements for the degree of Doctor of Philosophy.

#### 11.06.2020

| Head of Committee | Prof. Minkyu Je     | (signature) |

|-------------------|---------------------|-------------|

| Committee Member  | Prof. Junghyup Lee  | (signature) |

| Committee Member  | Prof. Jaeeun Jang   | (signature) |

| Committee Member  | Prof. Jiwoong Choi  | (signature) |

| Committee Member  | Prof. Jaeyoun Hwang | (signature) |

Ph.D/IC 201532005

홍 순 영. Soonyoung Hong. Ultra-low Power Receiver Based on an Injection Locked Oscillator. Department of Information and Communication Engineering. 2021. 100p. Advisors Prof. Junghyup Lee, Co-Advisors Prof. Minkyu Je

#### **ABSTRACT**

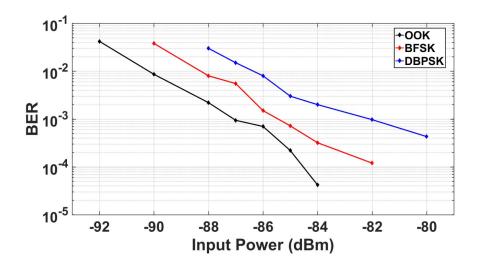

This thesis presents an ultra-low-power receiver based on the injection-locked oscillator (ILO), which is compatible with multiple modulation schemes such as on-off keying (OOK), binary frequency-shift keying (BFSK), and differential binary phase-shift keying (DBPSK). The receiver has been fabricated in 0.18 µm CMOS technology and operates in the ISM band of 2.4 GHz. A simple envelope detection can be used even for the demodulation of BFSK and DBPSK signals due to the conversion capability of the ILO from the frequency and phase to the amplitude. In the proposed receiver, a Q-enhanced single-ended-to-differential amplifier is employed to provide high-gain amplification as well as narrow bandpass filtering, which improves the sensitivity and selectivity of the receiver. In addition, a gain-control loop is formed in the receiver to maintain constant lock range and hence frequency-to-amplitude conversion ratio for the varying power of the BFSK-modulated receiver input signal. The receiver achieves the sensitivity of –87, –85, and –82 dBm for the OOK, BFSK, and DBPSK signals respectively at the data rate of 50 kbps and the BER lower than 0.1 % while consuming the power of 324 µW in total

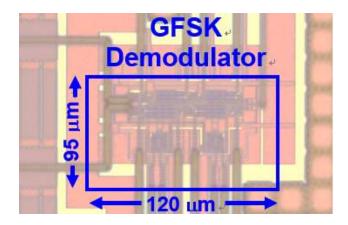

This thesis presents an ultra-low power, low cost demodulator for gaussian frequency shift keying (GFSK) receivers that use low intermediate frequencies (IF). The demodulator employs a direct IF to digital data conversion scheme by using an injection-locked ring oscillator (ILRO) with a 1-bit flip-flop. It consumes  $2.7~\mu W$  from a 1.0~V supply at a data rate of 500~kbps achieving an energy efficiency of 5.4~pJ/bit which is 30~times better than that of the recently presented works. The demodulator also achieves 17.5~dB SNR at 0.1~% BER while operating at the same date rate. The demodulator is implemented in a  $0.18~\mu m$  standard CMOS process and occupies an active area of  $0.012~mm^2$ .

Keywords: Ultra-low power, injection-locked oscillator, injection-locking receiver, multi-modulation, frequency-to-amplitude conversion, phase-to-amplitude conversion, wireless sensor node, internet of things, single-ended-to-differential conversion, Q enhancement, envelope detection, Demodulator, GFSK, low power, low-IF, CMOS.

# List of Contents

| A      | bstract·····i                                            |

|--------|----------------------------------------------------------|

| L      | ist of contents ····ii                                   |

| L      | ist of tables ·····iii                                   |

| L      | ist of figures ······vi                                  |

|        |                                                          |

| I. Int | troduction ······1                                       |

|        | 1.1 Motivation ·····1                                    |

|        | 1.2 Design Considerations of Receiver ······4            |

|        | 1.3 Conventional Architecture ······                     |

|        | 1.4 Proposed Structure ······ 12                         |

|        | 1.5 Overview of the thesis · · · · · · 15                |

|        |                                                          |

| II. Ir | njection Locked Oscillator16                             |

|        | 2.1 Operation Principle 17                               |

|        | 2.1.1 Injection Locked LC Oscillator · · · · · 17        |

|        | 2.1.2 Injection Locked Ring Oscillator ····· 22          |

|        | 2.2 Conversion Process of Injection Locked Oscillator 27 |

|        | 2.2.1 Amplitude to Amplitude Conversion ····· 27         |

|        | 2.2.2 Frequency to Amplitude Conversion · · · · · 28     |

|        | 2.2.3 Phase to Amplitude Conversion · · · · · 29         |

|        | 2.2.4 Frequency to Phase Conversion                      |

|        | 2.3 Summary 39                                           |

|        |                                                          |

| III.   | A Multi-Mode ULP Receiver Based on an Injection          |

|        |                                                          |

|        | Locked LC Oscillator · · · · · · 40                      |

| 3                    | .1 Overall Receiver Architecture ······· 40                                                                                                                                           |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3                    | .2 Details of the Blocks ······ 43                                                                                                                                                    |

|                      | 3.2.1 Pre-amplifier                                                                                                                                                                   |

|                      | 3.2.2 Single to differential amplifier · · · · · 48                                                                                                                                   |

|                      | 3.2.3 Injection Locked LC oscillator 56                                                                                                                                               |

|                      | 3.2.4 Fully Differential Envelope Detector 59                                                                                                                                         |

|                      | 3.2.5 Base-band Amplifier 62                                                                                                                                                          |

|                      | 3.2.6 Fully Differential Comparator 64                                                                                                                                                |

|                      | 3.2.7 Peak Detector                                                                                                                                                                   |

| 3                    | .3 Experimental Results · · · · · 72                                                                                                                                                  |

| 3                    | .4 Summary 82                                                                                                                                                                         |

|                      |                                                                                                                                                                                       |

|                      | low Power GFSK Demodulator Based on an Injection ked Ring Oscillator83                                                                                                                |

| Loc                  | ·                                                                                                                                                                                     |

| <b>Loc</b><br>4      | ked Ring Oscillator ····· 83                                                                                                                                                          |

| <b>Loc</b><br>4      | ked Ring Oscillator       83         .1 Overall Demodulator Architecture       85                                                                                                     |

| <b>Loc</b><br>4      | ked Ring Oscillator 83  1 Overall Demodulator Architecture 85  2 Details of the Blocks 87                                                                                             |

| <b>Loc</b><br>4<br>4 | ked Ring Oscillator83.1 Overall Demodulator Architecture85.2 Details of the Blocks874.1.1 Pulse Slicer87                                                                              |

| <b>Loc</b><br>4<br>4 | ked Ring Oscillator83.1 Overall Demodulator Architecture85.2 Details of the Blocks874.1.1 Pulse Slicer874.1.2 Injection Locked Ring Oscillator88                                      |

| <b>Loc</b><br>4<br>4 | ked Ring Oscillator83.1 Overall Demodulator Architecture85.2 Details of the Blocks874.1.1 Pulse Slicer874.1.2 Injection Locked Ring Oscillator88.3 Experimental Results91             |

| Loc<br>4<br>4<br>4   | ked Ring Oscillator83.1 Overall Demodulator Architecture85.2 Details of the Blocks874.1.1 Pulse Slicer874.1.2 Injection Locked Ring Oscillator88.3 Experimental Results91             |

| Loc 4 4 V. Conc      | ked Ring Oscillator83.1 Overall Demodulator Architecture85.2 Details of the Blocks874.1.1 Pulse Slicer874.1.2 Injection Locked Ring Oscillator88.3 Experimental Results91.4 Summary96 |

## List of tables

| Table 1.1 Comparison of Characteristics of Receiver Architecture · · · · · · · · · 1 |

|--------------------------------------------------------------------------------------|

| Table 1.2 Target Specification of Proposed Receiver System                           |

| Table 2.1 Sapling State According to the Phase Difference                            |

| Table 3.1 Power Breakdown of the Receiver 80                                         |

| Table 3.2 Performance Summary and Comparison with Previous Works                     |

| Table 4.1 Power Breakdown of the Demodulator ·····9                                  |

| Table 4.2 Performance Comparison99                                                   |

# List of figures

| Figure 1.1 Conceptual block diagram of wireless sensor node for IoT                                                 |

|---------------------------------------------------------------------------------------------------------------------|

| Figure 1.2 Tuned-RF receiver (a) block diagram (b) operation 6                                                      |

| Figure 1.3 Low-IF receiver. 7                                                                                       |

| Figure 1.4. Super-regenerative receiver (a) block diagram (b) operation                                             |

| Figure 1.5 Uncertain-IF receiver (a) block diagram (b) operation9                                                   |

| Figure 1.6 Injection locking receiver                                                                               |

| Figure 1.7 Overall architecture of the proposed wireless receiver system                                            |

| Figure 1.8 Input and output waveform of (a) OOK (b) BFSK (c) DPSK13                                                 |

| Figure 2.1 (a) Conceptual diagram of ILO, and (b) frequency response of LC tank 17                                  |

| Figure 2.2 Phasor diagrams of ILO currents when the ILO (a) runs freely, (b) ex-                                    |

| periences locking transition, (c) is locked, and (d) operates at the edge                                           |

| of its lock range. · · · · · 18                                                                                     |

| Figure 2.3 Phase diagrams of the different currents (a) arbitrary $\theta 0$ (b) $\phi 0$ ,max                      |

| Figure 2.4 N-stage injection locked ring oscillator (a) frequency response of the                                   |

| delay cell (b) and a phase diagram for injection locking (c)                                                        |

| Figure 2.5 Phasor diagrams of ILO currents for the OOK-modulated injection sig-                                     |

| nal when: (a) $I_{inj}$ is on and (b) $I_{inj}$ is off. $\cdots 27$                                                 |

| Figure 2.6 Phasor diagrams of injection locked LC oscillator currents for the FSK                                   |

| modulated injection signal when: (a) $\omega_{inj} = \omega_a \approx \omega_0$ and (b) $\omega_{inj} = \omega_b =$ |

| $\omega_a + \Delta \omega$                                                                                          |

| Figure 2.7 Phasor diagrams of injection locked LC oscillator currents for the PSK                                   |

| modulated injection signal when: (a) $\theta_{inj} = \theta_0$ and (b) $\theta_{inj} = \theta_0 + \pi$              |

| Figure 2.8 Change of 4-stage ILRO output according to injection position rising                                     |

| edge (a), falling edge (b), high state (c) and low state (d)32                                                      |

| Figure 2.9 Injection-locking transient responses at $f_{INJ} = f_0$ (a), $f_{INJ} < f_0$ (b) and                    |

| $f_{INJ} > f_0$ (c)34                                                                                               |

| Figure 2.10 Phase-relationships with the sampling edge at $f_{INI} < f_0$ (a) and                                   |

| $f_{INI} > f_0$ (b)                                                                                                 |

| Figure 3.1 Overall architecture of the proposed wireless receiver system40                                          |

|                                                                                                                     |

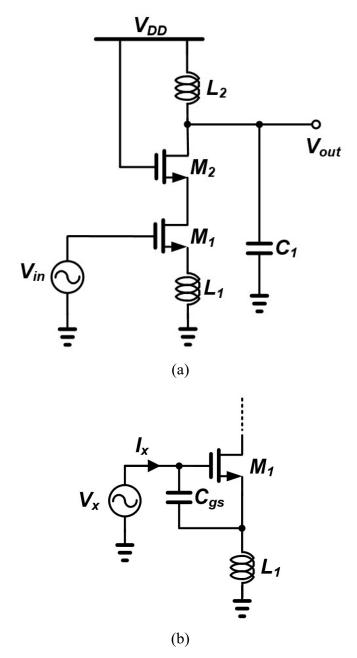

| Figure 3.2 Pre-amplifier of the proposed wireless receiver (a) schematic (b) input |

|------------------------------------------------------------------------------------|

| impedance of cascode amplifier. 44                                                 |

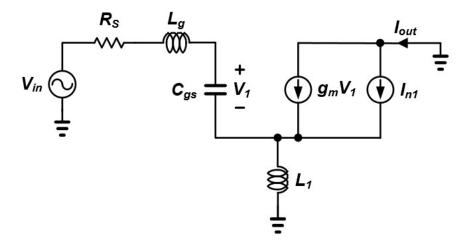

| Figure 3.3 Equivalent circuit of common-source stage for NF calculation46          |

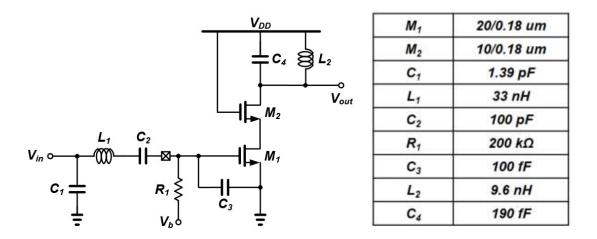

| Figure 3.4 Proposed pre-amplifier. 47                                              |

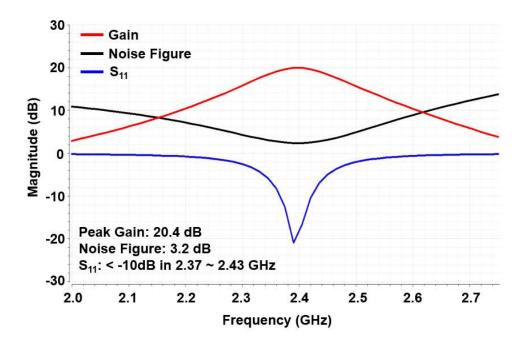

| Figure 3.5 Simulation Result of pre-amplifier. 47                                  |

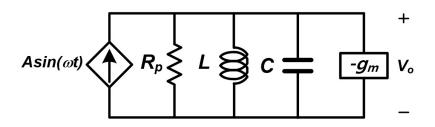

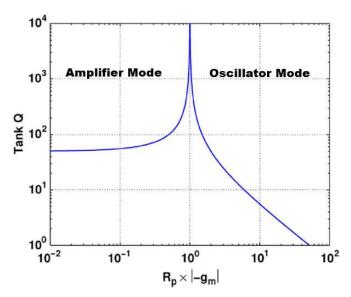

| Figure 3.6 Conceptual schematic of an LC oscillator with LC tank and negative      |

| conductance. 49                                                                    |

| Figure 3.7 Tank Q for varying negative trans-conductance and a fixed $R_p$         |

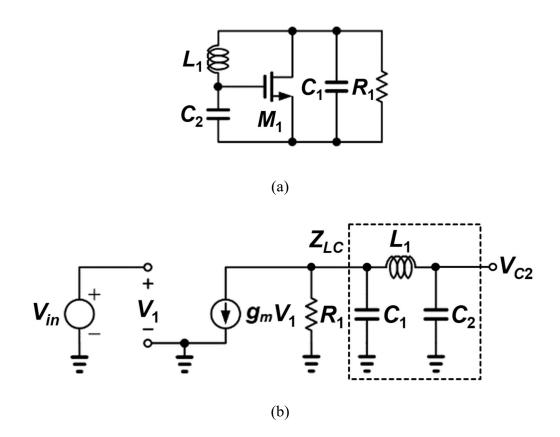

| Figure 3.8 Oscillator structure (a) parallel oscillation circuit (b) small-signal  |

| equivalent circuit of parallel oscillator 52                                       |

| Figure 3.9 Transfer function (a) Phase vs. frequency characteristic of the voltage |

| division factor and (b) magnitude vs. frequency characteristic of the              |

| loop gain 53                                                                       |

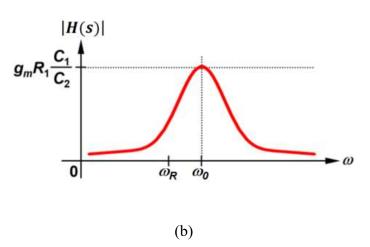

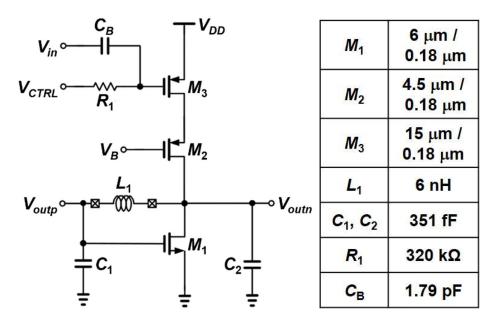

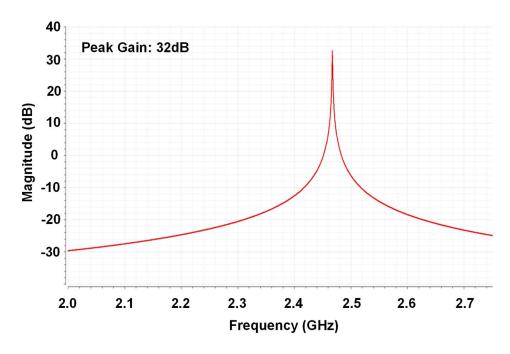

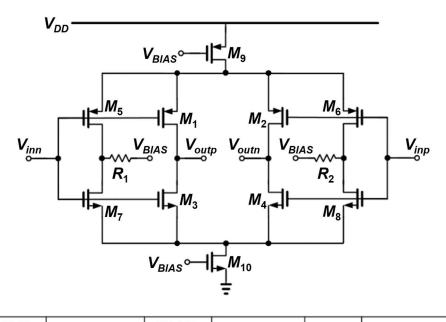

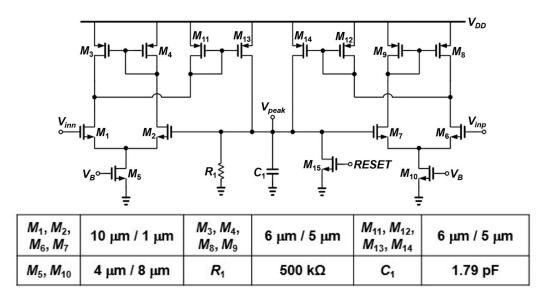

| Figure 3.10 Schematic diagram of the SDA                                           |

| Figure 3.11 Gain of SDA 55                                                         |

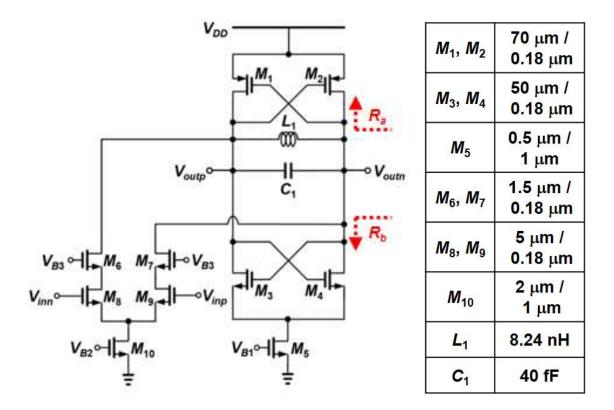

| Figure 3.12 Schematic diagram of the ILO 57                                        |

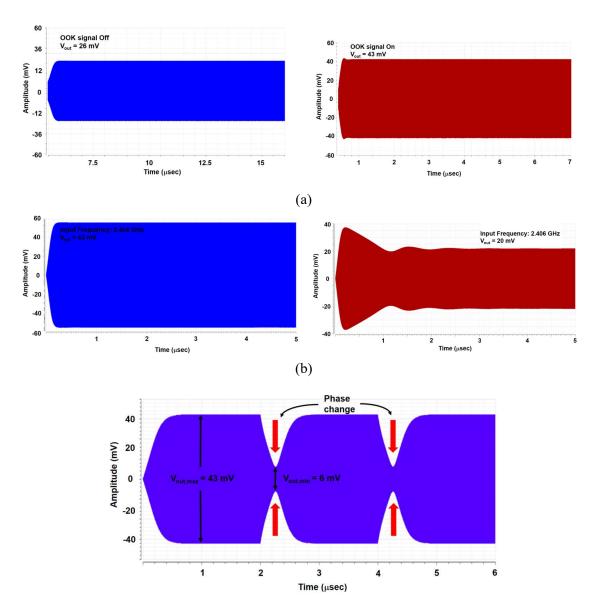

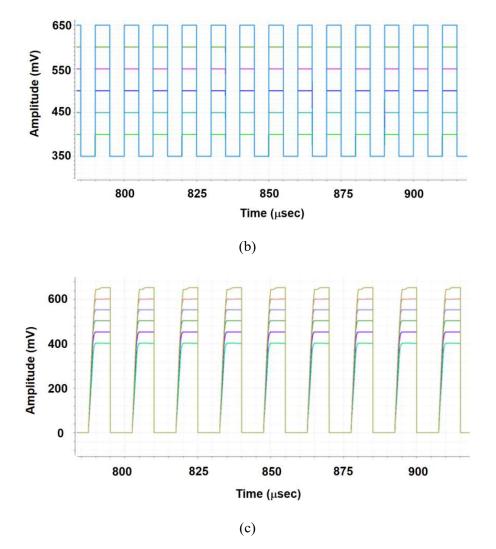

| Figure 3.13 Simulation results: (a) OOK mode (b) BFSK mode (c) DPSK mode 58        |

| Figure 3.14 Schematic of the proposed fully differential ED60                      |

| Figure 3.15 Transient simulation of envelope detector                              |

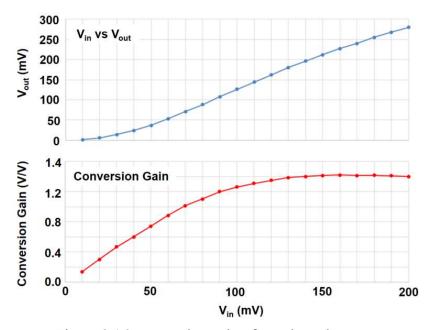

| Figure 3.16 Conversion gain of envelope detector                                   |

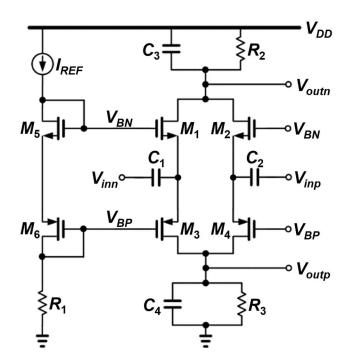

| Figure 3.17 Schematic of fully differential amplifier                              |

| Figure 3.18 BB AMP (a) schematic for simulation (b) simulation result              |

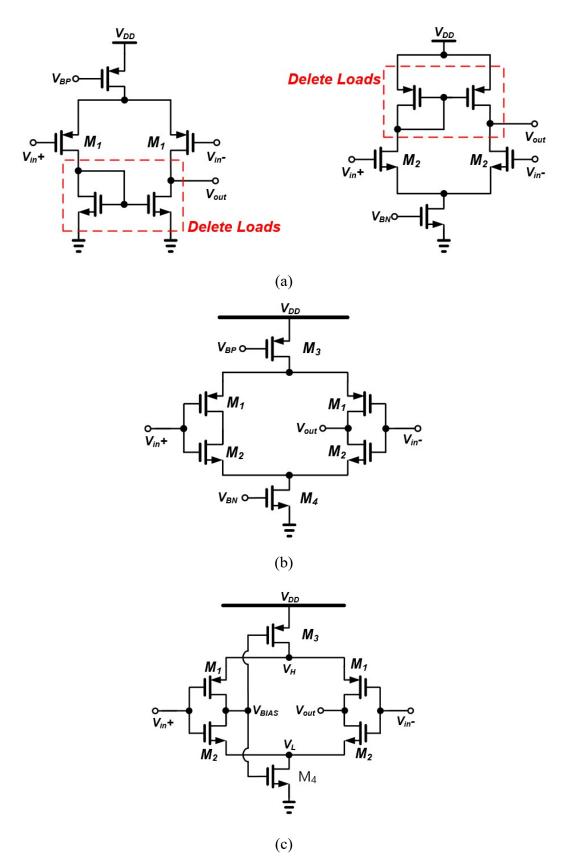

| Figure 3.19 Derivation of complementary self-bias amplifier (a) conventional am-   |

| plifier (b) external bias amplifier (c) complementary self-bias ampli-             |

| fier 65                                                                            |

| Figure 3.20 Schematic diagram of the fully differential comparator. 66             |

| Figure 3.21 Simulation result of fully differential comparator. 67                 |

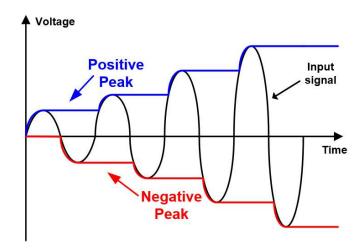

| Figure 3.22 Ideal peak detector outputs                                            |

| Figure 3.23 Positive peak detector using current mirror                            |

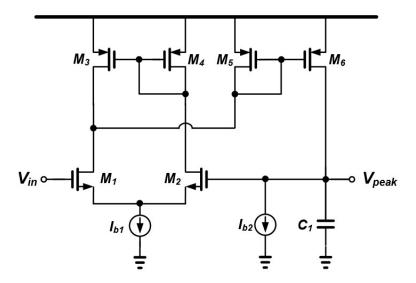

| Figure 3.24 Schematic of a peak detector for proposed receiver70                   |

| Figure 3.25 Simulation result of peak detector (a) input (b) output                |

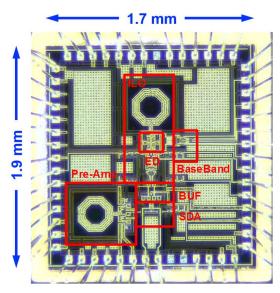

| Figure 3.26 Chip micrograph of the fabricated receiver IC                          |

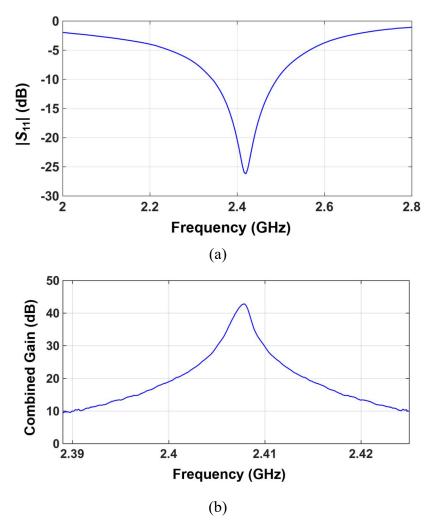

| Figure 3.27 (a) Impedance matching characteristic of the receiver (b) combined           |

|------------------------------------------------------------------------------------------|

| gain of the Pre-AMP and Q-enhanced SDA. · · · · · · · · · · · · · · · · · · ·            |

| Figure 3.28 (a) Baseband data of the receiver input and the corresponding ILO            |

| output waveforms for the receiver input modulated by (b) OOK, (c)                        |

| BFSK, and (d) DBPSK schemes75                                                            |

| Figure 3.29 Demodulated output data of the receiver ···································· |

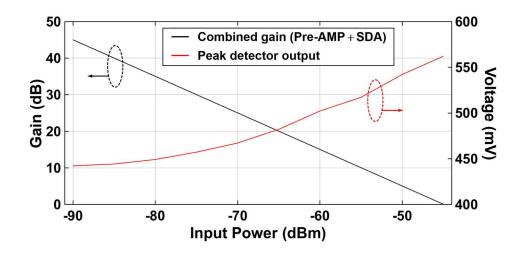

| Figure 3.30 SDA gain control characteristic as a function of the receiver input power 77 |

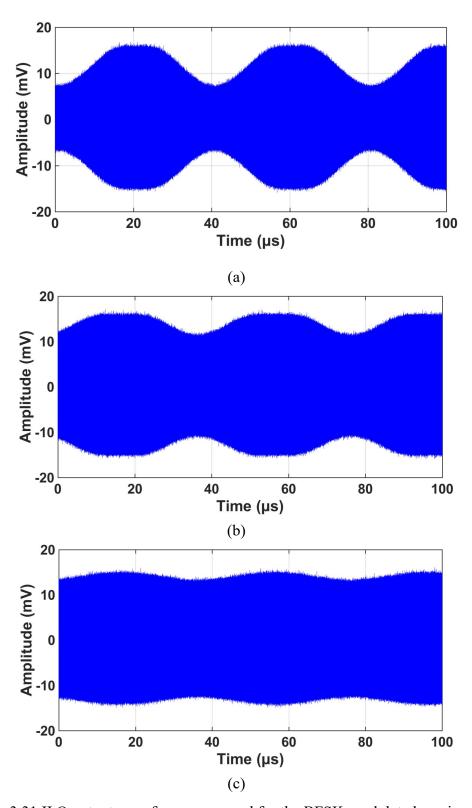

| Figure 3.31 ILO output waveforms measured for the BFSK-modulated receiver                |

| input signal with different power levels: (a) -70 dBm, (b) -66 dBm,                      |

| and (c) -64 dBm, when the SDA gain control loop is disabled. · · · · · · · · · · 78      |

| Figure 3.32 BER performance of the proposed receiver measured with the data-             |

| rate of 50 kb/s as a function of the input power                                         |

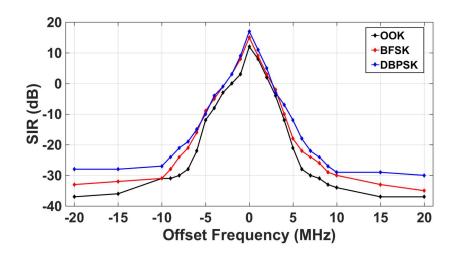

| Figure 3.33 SIR performance of the proposed receiver measured with the data rate         |

| of 50 kb/s and the 6-dB higher input power than the sensitivity limit 80                 |

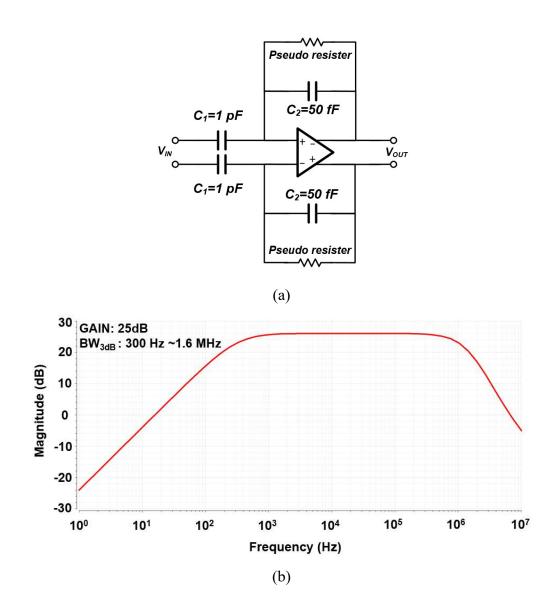

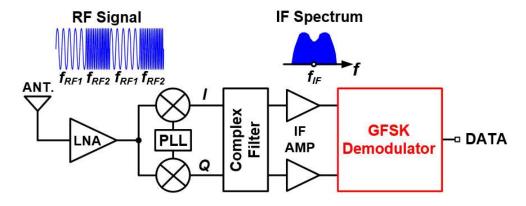

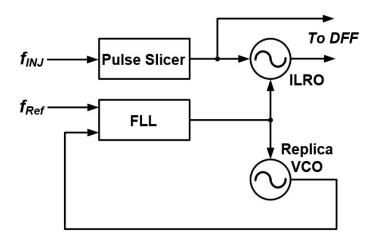

| Figure 4.1 Overall structure of a GFSK receiver with a low IF84                          |

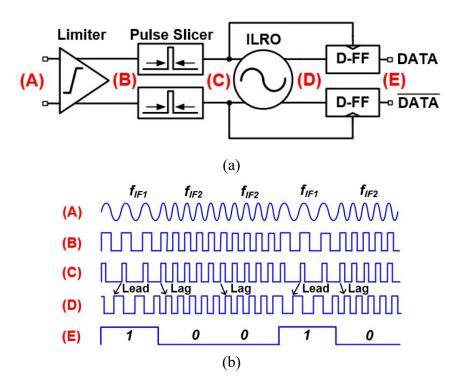

| Figure 4.2 Block diagram and timing waveforms of the proposed ILRO based                 |

| GFSK demodulator86                                                                       |

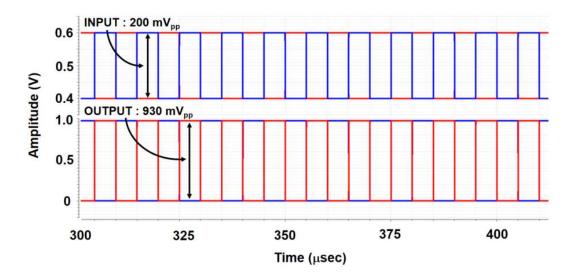

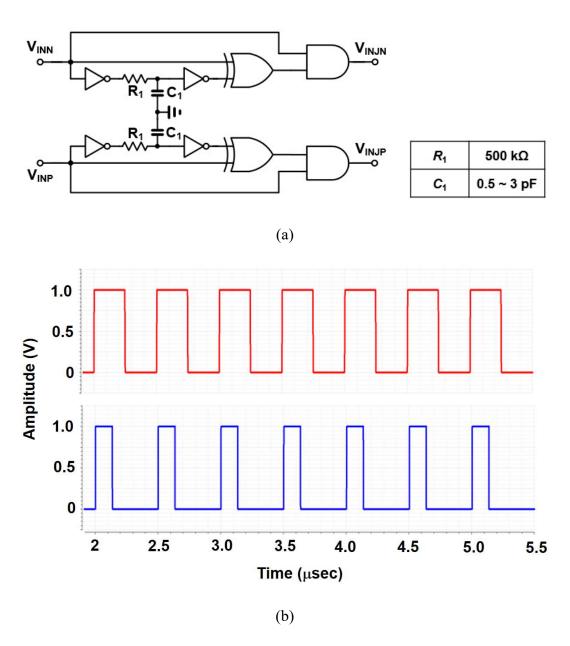

| Figure 4.3 Pulse slicer (a) schematic (b) input and output waveform. 87                  |

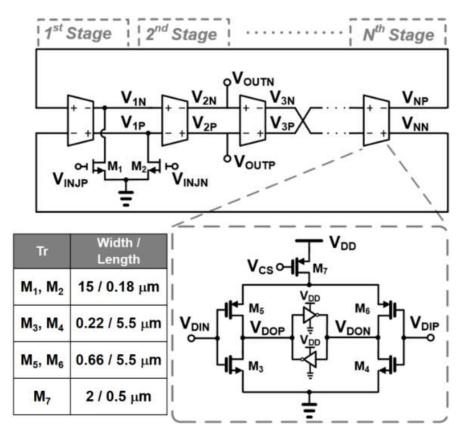

| Figure 4.4 Schematic of the differential ILRO89                                          |

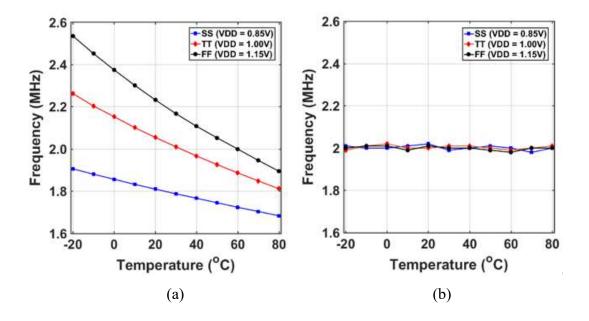

| Figure 4.5 Change of free-running frequency of ILRO according to PVT (a) be-             |

| fore calibration (b) after calibration                                                   |

| Figure 4.6 ILRO with frequency locked loop (FLL) using a replica VCO90                   |

| Figure 4.7 Chip micrograph of GFSK demodulator. 91                                       |

| Figure 4.8 Simulation results of 4-stage differential ILRO at $f_{INJ} < f_0$ (a) and    |

| $f_{INJ} > f_0$ (b)92                                                                    |

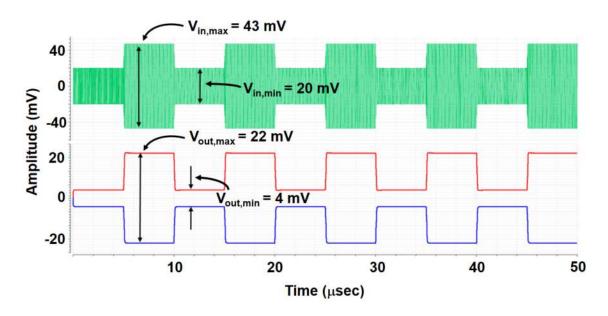

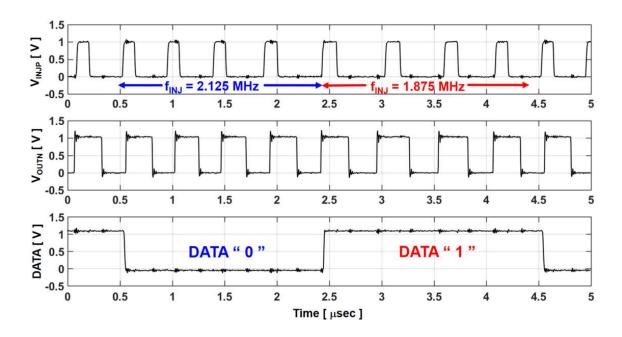

| Figure 4.9 Measured GFSK demodulator responses93                                         |

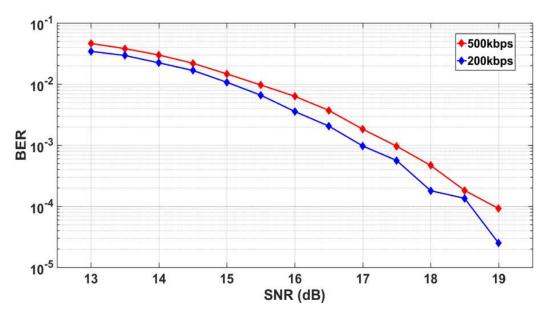

| Figure 4.10 Measured BER performances of the GESK demodulator                            |

# I. INTRODUCTION

#### 1.1 Motivation

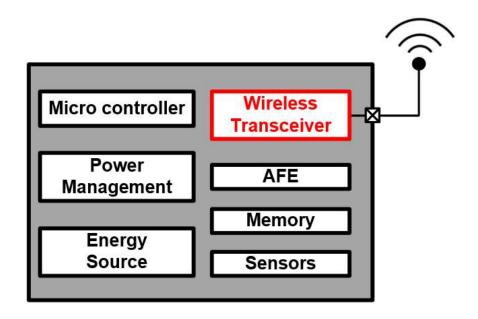

Figure 1.1 Conceptual block diagram of wireless sensor node for IoT.

As a variety of services and applications based on the internet of things (IoT) have been widely developed, the demands on ultra-low power (ULP) wireless techniques for data transmission and reception have grown rapidly. The capability of performing wireless communication with little power consumption is a key factor enabling the operation of ubiquitous sensor nodes (USN) for IoT [1]. As the complexity and scale of the IoT system increases and the number of sensor nodes in the network becomes large, connecting the sensor nodes to the power lines makes the installation of the system prohibitively expensive if not impossible. It is therefore preferred to power the sensor nodes by batteries. In such battery-powered sensor nodes, low power consumption is an essential requirement considering that the power consumption of the sensor node determines the replacement or

recharging frequency of the battery and directly affects the maintenance cost of the IoT system.

Furthermore, to realize the vision of the hyper-connected world filled with trillions of sensor nodes, researchers are working toward the energy-autonomous operation of the wireless sensor nodes, which are powered by the energy harvested from their ambience. In this scenario, the average power consumption of the overall sensor node must be lower than the average rate of energy harvesting. It poses extreme limitations on the power budget of the wireless sensor node, even if the duty-cycled operation scheme is employed to cut down the amount of the power dissipated on average. Since the wireless transceiver is the most power-hungry block in the typical wireless sensor node as shown in Fig. 1.1, reducing the power consumed for wireless communication is critical.

On the other hand, the choice of modulation scheme has a significant impact on the transceiver design in various aspects such as power consumption, complexity, performance, and reliability. For short-range low-power communication, the transceivers based on onoff keying (OOK) have been widely implemented. The OOK modulation scheme allows achieving very low power consumption because of the simple circuit architecture used for the transceiver design. For example, the demodulation function of the receiver can be implemented by using an envelope detector without requiring any high-power-consuming circuit components such as oscillators, mixers, and frequency synthesizers [2]–[4]. However, the OOK receiver based on such a simple structure has low sensitivity and high susceptibility to the interferers compared to the receivers employing other modulation schemes such as frequency-shift keying (FSK) and phase-shift keying (PSK). To overcome the limited sensitivity performance, a high-gain amplifier and an expensive external

filter are required to precede the envelope detector [2]. The FSK modulation with a constant envelope, on the other hand, enables the use of an energy-efficient nonlinear power amplifier in the transmitter. However, the receiver requires the precise local oscillator and quadrature signal paths, which results in a complex receiver structure consuming relatively high power.

Hence, it is essential to investigate ULP wireless receiver used in wireless sensor node for IoT while overcoming the limitation of the receiver performance according to modulation schemes. In this thesis, the ULP wireless receiver which can support multiple modulation schemes and ultra-low power Gaussian FSK (GFSK) demodulator based on a signal conversion scheme of an injection locking technic are proposed and demonstrated.

### 1.2 Design Consideration of Receiver for Internet of Things

Generally, the requirements of receiver depend on the application of interest. In wireless sensor node for IoT applications, battery life, capacity, communication distance and compatibility should be key considerations as well. For the realization of wireless sensor nodes used in IoT, the implementation of receivers used in each sensor node should optimize the following four characteristics.

- Low Power Consumption: The Power consumption determines the size of the battery installed or integrated and the lifetime of the sensor node. Mechanisms to reduce power consumption improve the lifetime of the wireless sensor node

- High Sensitivity: The sensitivity of receiver in sensor node is related to the power consumption of transmitter and communication distance.

- High Channel Selectivity: The higher channel selectivity of the receiver can form many channels between numerous sensor node within the assigned frequency band.

- High Compatibility with Wireless Standards: The use of wireless standards can improve compatibility between wireless sensor node and other wireless devices.

A wireless transceiver is the most power-hungry block in the sensor node as mentioned above. If the power consumption of the components consist of the transceiver is minimized, the sensor node used for IoT can extend the lifetime or reduce the size of the battery. Therefore, in order to improve the lifetime of the sensor node used for IoT, the low power design should be the top priority.

Secondly, if the sensitivity of receiver in the sensor node is improved, the transmission power of the transmitter can be reduced. Thereby, the transmitter consumes relatively low power. That results in an extended communication range consuming same power.

In the receivers used in IoT application, each sensor node forms a network and communicates with each other. So, a high channel selectivity is required for multi-channel operation.

In order to use the existing well-defined communication network, a communication between wireless devices and sensor node is possible by using a suitable wireless standard. For example, Currently, wireless communication standards such as Bluetooth using FSK, Zig-bee using PSK, and RFID using ASK are typical.

The injection locked oscillator (ILO) in the proposed receiver in this thesis allows to use of a simple envelope detection circuit which can reduce total power consumption of receiver. Also, the Q-enhanced single-ended-to-differential amplifier (SDA) is employed to provide high sensitivity and high selectivity. Furthermore, the proposed receiver is suitable for a variety of modulation schemes such as OOK, FSK, PSK by using signal conversion characteristic of ILO.

#### 1.3 Conventional Architecture

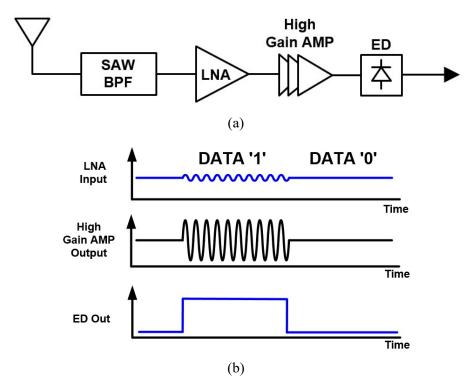

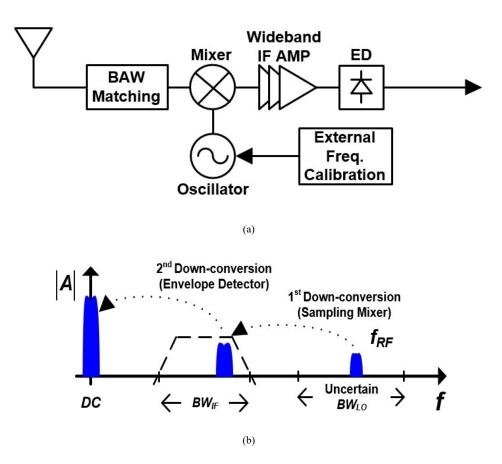

Figure 1.2 Tuned-RF receiver (a) block diagram (b) operation.

Recently, to overcome the limitations of the conventional receivers, a variety of new receiver structures for ultra-low power (ULP) consumption have been introduced. However, most of the developed receivers have several drawbacks to use in the IoT network mentioned above. Most of the recent low-power receivers employ an envelope detection architecture with OOK modulation because of its simplicity which leads to the best power efficiency.

The tuned-RF architecture which has a very simple structure is shown in Fig. 1.2 (a). The received input signal should be amplified before applying envelope detector (ED) to improve the sensitivity of the receiver. Achieving such amplification at minimal power consumption has been the main design target of the recently proposed architectures. However,

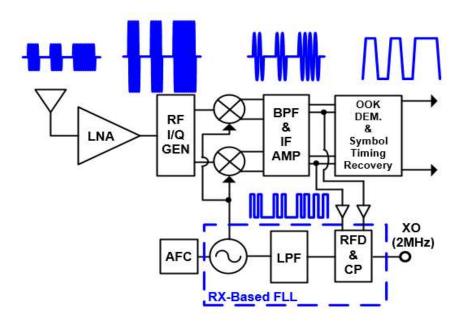

Figure 1.3 Low-IF receiver.

the front-end amplifier in the tuned RF architecture [2] consumes significantly larger power due to operating in the high frequency. Therefore, there is a limitation to achieve the high sensitivity in the given power budget. Additionally, to achieve the high selectivity, an external, discrete High-Q SAW filter is required. Such filters occupy a very large size and hence they increase the size and cost of the receiver.

Another conventional architecture is Low-IF. Fig. 1.3 shows the low-IF receiver structure, where the receive path itself operates as a part of the frequency-locked loop (FLL) for LO generation [5]. The Low-IF receiver architecture is resilient to DC offset and 1/f noise in comparison with a Zero-IF receiver architecture. Since the mixers in the receive path perform frequency down-conversion for not only receiver function but also FLL operation, the high-precision LO signal can be generated without using a power-hungry frequency divider. However, the structural complexity is high due to the FLL and quadrature demodulation circuits.

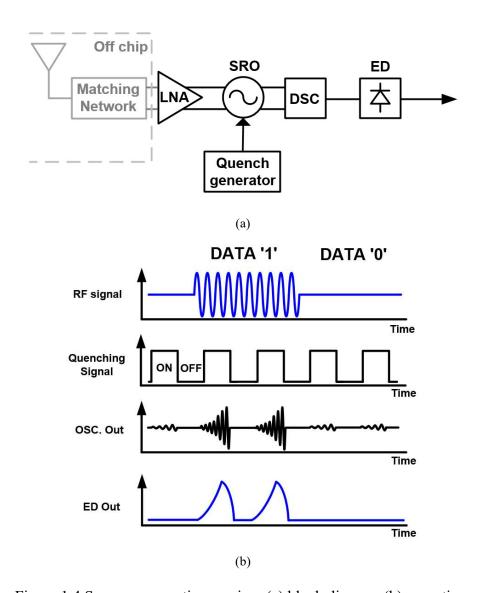

Figure 1.4 Super-regenerative receiver (a) block diagram (b) operation.

The super-regenerative receiver is not commonly used as super-heterodyne or direct conversion receiver architecture due to the low selectivity. Recently, however, due to its simple structure and low power consumption, the super-regenerative receiver is used in local area communication. Fig. 1.4(a) shows the receiver structure of the super-regenerative receiver for OOK modulation [6]. The output of the receiver is determined using a quenching signal and RF signal input to the super-regenerative oscillator (SRO).

Figure 1.5 Uncertain-IF receiver (a) block diagram (b) operation.

The operation of super-regenerative receiver is shown in Fig. 1.4(b). In accordance with the low frequency quenching signal, the super-regenerative oscillator is operated in an oscillating mode (quenching signal is high) or damping mode (quenching signal is low). When the RF signal with large amplitude is applied through the antenna and quenching signal is high, the output amplitude of the oscillator will very rapidly reach a steady state. Then, the output of ED goes high level. On the contrary, if the RF signal amplitude is low and quenching signal is high, the output amplitude of the oscillator cannot reaches a steady state. As a result, there is no change in the output of ED. Even though the RF signal with in the vicinity of free running frequency is applied to the SRO, the SRO makes steady state output signal. Therefore, the selectivity of this receiver is poor.

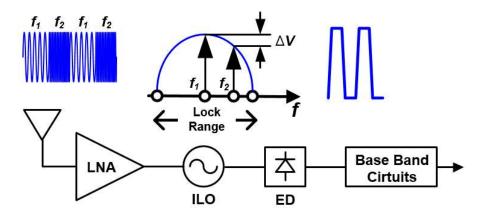

Figure 1.6 Injection locking receiver.

Fig. 1.5 shows the structure of the uncertain-IF receivers [7]. In this structure, a low-power free-running ring oscillator is used to generate the local oscillator (LO) signal for down-conversion. Due to the inherent uncertainty of the LO signal frequency, the IF frequency is not clearly determined, and the selectivity performance of the receiver is therefore low. Fig. 1.6 shows the receiver structure based on the injection-locked oscillator [8], [9]. The ILO plays an essential role of converting the frequency-modulated signal to the amplitude-modulated signal, which enables the energy-efficient implementation of the FSK receiver. The amplitude-modulated signal generated by the ILO is down-converted by the envelope detector as in the conventional low-power OOK receiver. This structure, however, faces significant challenges in that the amplitude of the signal injected to the ILO should be sufficiently large for guaranteeing proper injection-locking operation and kept relatively constant for maintaining consistent frequency-to-amplitude conversion ratio.

The receiver characteristics of the five recently published structure are summarized in Table 1.1 The tuned-RF and the uncertain-IF architecture has high selectivity due to the external High-Q filter. Even the Low-IF architecture has high complexity and low sensitivity, it reduces power consumption significantly using RX-path in a frequency

Table 1.1 Comparison of characteristics of receiver architecture

|             | Tuned-RF | Low-IF  | Uncertain- IF | Super<br>Regenerative | Injection<br>Locking |

|-------------|----------|---------|---------------|-----------------------|----------------------|

| Power       | Low      | Low     | Low           | Low                   | High                 |

| Sensitivity | Low      | High    | Low           | Low                   | Low                  |

| Selectivity | High     | Low     | High          | Low                   | Low                  |

| Simplicity  | Simple   | Complex | Simple        | Simple                | Simple               |

| Modulation  | ООК      | OOK     | OOK           | OOK                   | FSK                  |

locked loop circuit. The uncertain-IF receiver architecture is possible to reduce power consumption because it does not need an accurate, high quality local oscillator.

The super-regenerative receiver can reduce power consumption because of its simplicity. However, the selectivity and sensitivity is low due to the inherent characteristics of SRO. The injection-locking receiver consume a high-power. Because the high gain is required in front of ILO for the injection locking. Nevertheless, this receiver has an advantage that is robust against to the interferer compare with other receivers due to using a FSK modulation.

#### 1.4 Proposed Structure

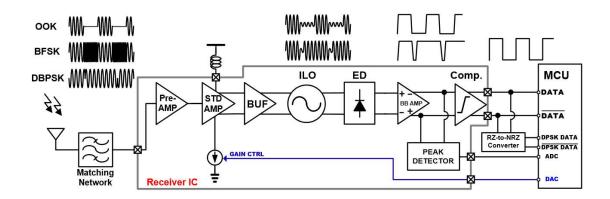

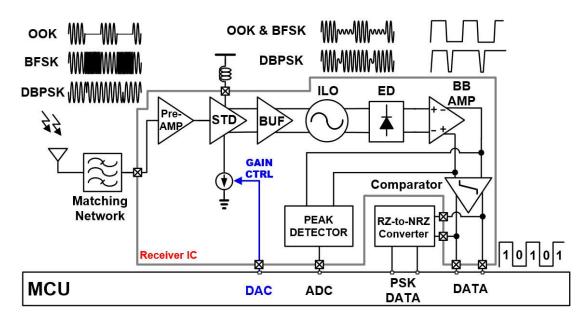

Figure 1.7 Overall architecture of the proposed wireless receiver system.

The block diagram of the proposed receiver is shown in Fig.1.7. The proposed receiver consist of the front-end matching network, RF receiver IC, and microcontroller unit (MCU). The pre-amplifier connected to the antenna through a matching network amplifies the RF signal. The Pre-AMP amplifies the RF signal with moderate gain and provides isolation between the matching network and the single-to-differential amplifier (SDA) input. The STD significantly improves the sensitivity of the overall receiver system by using Q-enhancement. The *Q*-enhancement technique is applied to the SDA so that high gain can be achieved over a narrow frequency band. The narrow band filtering effect provide high selectivity. In addition, the STD converts its single-ended input signal to differential signal that drives the injection locked LC oscillator.

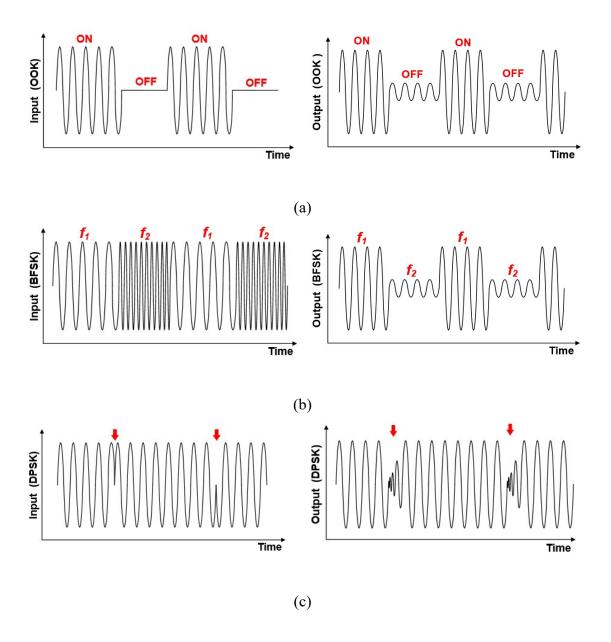

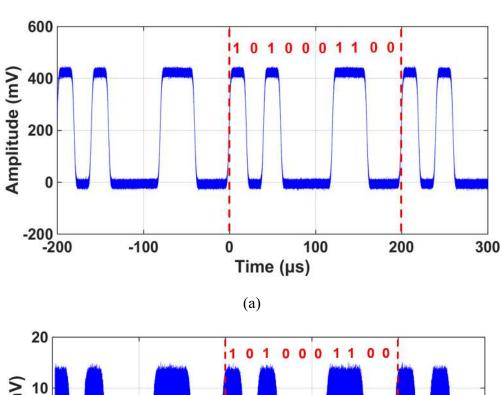

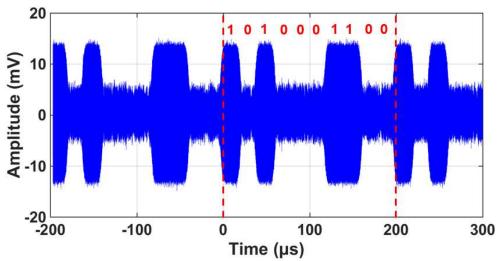

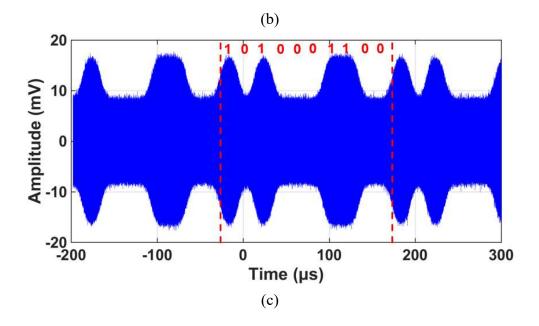

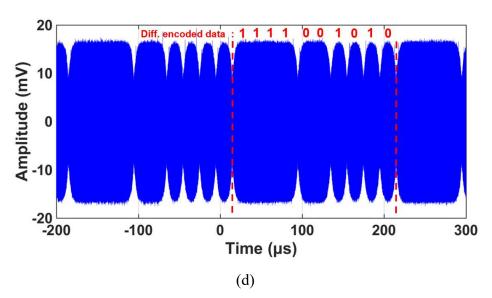

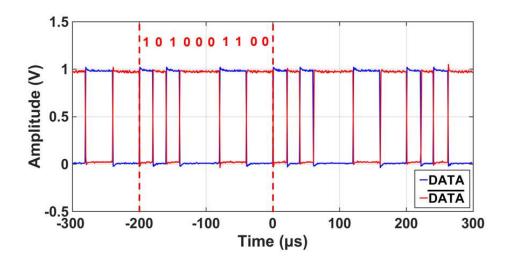

The output amplitude of the ILO changes depending on modulation scheme such as Fig. 1.8. For the OOK input signal as shown in Fig. 1.8 (a), the ILO simply adds the constant amount of signal amplitude as explained in Chapter II, and thus the amplitude variations of the input signal are preserved at the ILO output.

Figure 1.8 Input and output waveform of (a)OOK (b)BFSK (c)DPSK.

The BFSK signal as shown in Fig. 1.8 (b), ILO output has a large amplitude when the frequency of the injection signal ( $\omega_l$ ) is close to the free-running frequency of the ILO ( $\omega_0$ ), while the output amplitude becomes small when  $\omega_2$  is far from  $\omega_0$  as shown in Fig. 1.8 (b). In DPSK scheme such as Fig. 1.8 (c), the output amplitude is fluctuated such when the phase of injection current is shifted 180°.

Table 1.2 Target Specification of Proposed Receiver System

| Item                | Design goal      | Unit |

|---------------------|------------------|------|

| Operating Frequency | 2.4 GHz ISM band | -    |

| Modulation          | FSK(or OOK, PSK) | -    |

| Data Rate           | ≥ 10             | Kb/s |

| Sensitivity         | < -85            | dBm  |

| power consumption   | < 350            | μW   |

Hence, The ILO not only translates the OOK/BFSK/DBPSK signal to the amplitude-modulated signal but also improves the receiver sensitivity because the weak RF signal injected to the ILO generates the oscillator output signal having a relatively large swing.

The ILO output is down converted to a baseband signal by the envelope detector. The baseband signal is further amplified by a BB AMP. The BB AMP output is compared with a threshold of comparator and it generate the final data output.

The lock range of the ILO changes due to the varying magnitude of the injection signal, the frequency-to-amplitude conversion ratio doesn't stay constant. To keep constant lock range of ILO, input signal amplitude should be kept constant. So Peak detector capture output amplitude of BB AMP and amplitude information send to ADC of external MCU and DAC Block control the gain of STD. The target specification of proposed receiver system are summarized in Table 1.2.

#### 1.5 Overview of this Thesis

This thesis demonstrates a multi-mode ultra-low power receiver based on an ILO which achieves the high sensitivity and channel selectivity. These properties are provided by modulation conversion property of ILO, the Q-enhancement of SDA and auto gain control loop. In this thesis, a GFSK demodulator is also demonstrated using ILO. The frequency to phase conversion process of ILO is possible to use simple structure and to operate with ultra-low power. In chapter 1, the brief introduction of thesis is described. The preceding chapter provide the properties of conventional architectures and the overall architecture of the multi-mode ultra-low power receiver based on an ILO.

Chapter II focuses on the operating principle of ILO with LC and Ring type. Moreover, the detail of signal conversion process in the lock state of ILO is explained.

Chapter III introduces a multi-mode ultra-low power receiver based on an ILO which exploits the properties of ILO. This chapter include the detail of a low-power receiver design based on ILO, which can support multiple modulation schemes: OOK, binary FSK (BFSK), and differential binary PSK (DBPSK). A Q-enhanced SDA is employed to provide high gain and generate the injection signal with sufficient strength. Moreover, the consistency of the receiver performance is greatly improved by controlling the amplitude of the injection signal in a closed-loop manner.

The GFSK demodulator for low-IF receivers presented in in Chapter IV. This chapter presents the detail of the proposed demodulator architecture employing an ILO. Due to the frequency to phase conversion property, The proposed demodulator is able to use simple structure which consist of limiter, pulse slicer, ILO and D-flip flop. The simulation and chip measurement results of proposed demodulator explained this chapter. Then, the conclusion and further studies introduced in Chapter V.

## II. INJENTION LOCKED OSCILLATOR

When two systems with independent output frequencies are in close contact, the interaction between two systems can change the operating frequency of the two systems. Using two frequencies that are very close, but slightly different, the mutual influence can cause the two systems output one specific frequency. This phenomenon is called injection locking. However, the deviation between the two output frequencies is too large, injection pulling which the output signals pull each other in the frequency domain can occur. In this case, the output of the two systems varies in time domain. The frequency range for injection locking is defined as the lock range, and the two output signals are out of this range, injection pulling occurs.

Injection pulling is always considered an undesirable phenomenon because the output frequency of system changes over time. On the other hand, injection locking can be very useful in some applications. For example, there is a very low-noise signal with a well-defined output frequency, the stable oscillator output is obtained through inject locking by using this signal.

In this chapter, through a mathematical approach, the basic operation principle of the ILO according to the oscillator structure is presented. Mathematical equations are applied to the injection locking and pulling have been made and based on a study of Adler [10], Razavi [11]. Subsection 2.2 describes the conversion process between the injection signal and the output signal of the oscillator in the injection locking state.

## 2.1 Operating Principle

### 2.1.1 Injection Locked LC Oscillator

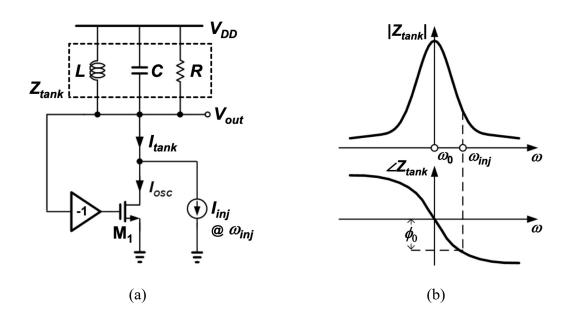

Figure 2.1 (a) Conceptual diagram of ILO, and (b) freuquency response of LC tank.

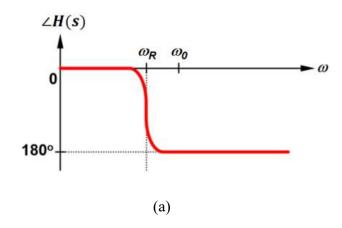

When the Injection signal has similar frequency to the oscillation frequency (resonance frequency of the LC Tank) is injected into oscillator, the output signal is synchronized to Injection signal. Hence, the frequency of output signal becomes same frequency with injection signal. The operation of injection-locked LC oscillator is described in Fig. 2.1. Fig. 2.1 (a) shows the conceptual diagram of the injection-locked LC oscillator. In the injection-locked LC oscillator, for the oscillation to sustain, the total phase shift of the loop  $(\angle H)$  must be a multiple of  $2\pi$  and magnitude of loop gain (|H|) must be larger than 1, as to meet the Barkhausen criteria [11]. In Fig. 2.1 (a), |H| and  $\angle H$  can be described as follow:

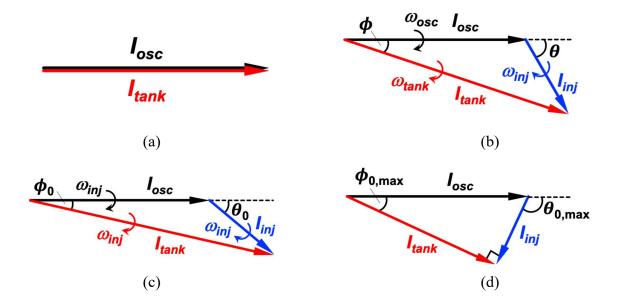

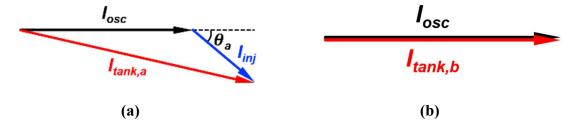

Figure 2.2 Phasor diagrams of ILO currents when the ILO (a) runs freely, (b) experiences locking transition, (c) is locked, and (d) operates at the edge of its lock range.

$$|H(s = j\omega_0)| = g_m R \ge 1 \tag{2.1}$$

$$\angle H(s = j\omega_0) = 360^{\circ} \tag{2.2}$$

At  $\omega_0$ , the  $Z_{tank}$  contributes no phase shift, as illustrated in Fig. 2.1 (b), while the inverting buffer and  $M_I$  create a total phase shift of 360°. The oscillation frequency is defined by [12],

$$\omega_0 = \frac{1}{\sqrt{L_1 C_1}} \tag{2.3}$$

In the free-running condition, the magnitude and phase of  $I_{tank}$  are the same as those of  $I_{osc}$ , as shown in Fig. 2.2 (a).

Now assume that the injection current  $I_{inj}$  having the frequency of  $\omega_{inj}$  is applied to the ILO. Since the  $I_{tank}$  should be the vector sum of  $I_{osc}$  and  $I_{inj}$ , the relationship among  $I_{osc}$ ,

Figure 2.3 Phase diagrams of the different currents (a) Arbitrary  $\phi_0$  (b)  $\phi_{0,\text{max}}$ .

$I_{inj}$ , and  $I_{tank}$  can be described by the phasor diagram as in Fig. 2.2 (b). Before locking, the phasors,  $I_{osc}$ ,  $I_{inj}$ , and  $I_{tank}$  rotates clockwise with different angular velocities,  $\omega_{osc}$ ,  $\omega_{inj}$ , and  $\omega_{tank}$ , respectively. Hence, the angle  $\theta$  between  $I_{osc}$  and  $I_{inj}$ , as well as the angle  $\phi$  between  $I_{osc}$  and  $I_{tank}$ , varies over time. After this transition process, if  $I_{inj}$  is not too small and  $\omega_{inj}$  is not too far from  $\omega_0$  to achieve injection-locking, the angle between the  $I_{osc}$  and  $I_{tank}$  becomes  $\phi_0$ , as shown in Fig. 2.2 (c), and this phase difference is compensated by the phase shift of  $Z_{tank}$ , as described in Fig. 2.1 (b). It makes the total phase shift around the feedback loop become  $360^{\circ}$ , and thus the ILO locked to the injection signal. Once injection-locked, the phasors  $I_{osc}$ ,  $I_{inj}$ , and  $I_{tank}$  rotate with the same angular velocity of  $\omega_{inj}$ , keeping  $\phi$  and  $\theta$  constant at  $\phi_0$  and  $\theta_0$ , respectively [11].

As the frequency of injection signal ( $\omega_{inj}$ ) deviates farther from the self-resonance frequency of the ILO ( $\omega_0$ ), the phase shift introduced by  $Z_{tank}$  ( $\phi_0$ ) grows, as found in Fig. 2.1 (b), and the angle between  $I_{osc}$  and  $I_{tank}$ , which is depicted in Fig. 2.2 (c), becomes larger. If  $\omega_{inj}$  keeps departing from  $\omega_0$  and finally reaches the edge of the lock range  $\omega_L$ , the angle between the  $I_{osc}$  and  $I_{tank}$  reaches a maximum and will thus limit the lock range. For find

out the phase relation of each component, we have to derive equation about  $\phi_0$  and  $\theta$ . Mathematical representation of the  $\phi_0$  can be derived using the law of sin, cos in Fig. 2.3 (a):

$$\sin \phi_0 = \frac{B}{I_{tank}}$$

and  $\sin \theta = \frac{B}{I_{inj}}$  (2.4)

$$\sin \phi_0 = \frac{I_{inj}}{I_{tank}} \sin \theta = \frac{I_{inj} \sin \theta}{\sqrt{I_{osc}^2 + I_{inj}^2 + 2I_{osc}I_{inj} \cos \theta}} = \sqrt{\frac{\frac{1 - \cos^2 \theta}{I_{osc}^2}}{I_{inj}^2} + 1 + 2\frac{I_{osc}}{I_{inj}} \cos \theta}}$$

(2.5)

For find out  $\phi_{0,\text{max}}$ , we can use differentiation.

$$\frac{dsin\phi_0}{dcos\theta} = \frac{1}{2} \cdot \left( \frac{\frac{I_{osc}^2}{I_{inj}^2} + 1 + 2\frac{I_{osc}}{I_{inj}} cos\theta}{1 - cos^2 \theta} \right)^{\frac{1}{2}} \cdot \frac{\left( \frac{I_{osc}^2}{I_{inj}^2} + 1 + 2\frac{I_{osc}}{I_{inj}} cos\theta \right) \cdot (-2co) - (1 - cos^2 \theta) \cdot \left( 2\frac{I_{osc}}{I_{inj}} \right)}{\left( \frac{I_{osc}^2}{I_{inj}^2} + 1 + 2\frac{I_{osc}}{I_{inj}} cos\theta \right)^2}$$

(2.6)

To find the maximum, this derivative has to be zero. The first term in above equation does not vanish so possible solutions have to be found in the second term.

$$2I_{osc}I_{inj}cos^{2}\theta + 2(I_{osc}^{2} + I_{inj}^{2})cos\theta + 2I_{osc}I_{inj} = 0$$

(2.7)

The two possible roots of this equation are

Soluition1:

$$cos\theta = -\frac{l_{inj}}{l_{asc}}$$

(2.8)

Soluition2:

$$cos\theta = -\frac{I_{osc}}{I_{inj}}$$

(2.9)

The second solution (2.9), however, results in  $sin\phi_0 = 1$  which means the tank should provide a phase shift of 90°. An RLC tank can only provide this shift for  $\omega \to \infty$  so the second solution (2.9) does not correspond to a real situation. The only solution (2.8) is thus

$$\sin \phi_{0,max} = \frac{I_{inj}}{I_{osc}} \quad for \quad \cos \theta = -\frac{I_{inj}}{I_{osc}}$$

(2.10)

The phase angle between  $I_{inj}$  and  $I_{osc}$  is  $90^{\circ} + \phi_{0,max}$ . If  $I_{inj}$  decreases,  $I_{osc}$  must form a greater angle as to maintain the phase difference between  $I_{tank}$  and  $I_{osc}$ . Thus, minimum injection level for locking is

$$I_{inj} \ge I_{osc} \cdot \sin \phi_{0,max} \tag{2.11}$$

To compute the value of corresponding to this case, we first note that the phase shift of the tank in the vicinity of resonance frequency. The transfer function of an RLC tank is given by

$$Z(j\omega) = \frac{j\omega L}{(1-\omega^2 LC) + \frac{j\omega L}{R}}$$

(2.12)

The phase characteristic thus equals

$$\angle Z(j\omega) = tan^{-1} \left( \frac{\omega L}{0} \right) - tan^{-1} \left[ \frac{\omega L}{R \left( 1 - \frac{\omega^2}{\omega_0^2} \right)} \right] = \frac{\pi}{2} - tan^{-1} \left[ \frac{\omega L}{R} \left( \frac{\omega_0^2}{\omega_0^2 - \omega^2} \right) \right]$$

(2.13)

This expression can be re-written using the following property of inverse trigonometric functions

$$\frac{\pi}{2} - tan^{-1}x = tan^{-1}(x)^{-1} \tag{2.14}$$

The nominator of the argument can be approximated via

$$\omega_0^2 - \omega = \omega_0^2 - [\omega_0 + (\omega - \omega_0)]^2$$

$$= -2(\omega - \omega_0)\omega_0 - (\omega - \omega_0)^2$$

$$\approx 2\omega_0(\omega_0 - \omega)$$

(2.15)

The approximate expression for the tangent of the phase eventually becomes

$$\tan \phi_0 = \frac{2Q}{\omega_0} \left( \omega_0 - \omega_{inj} \right) \tag{2.16}$$

From Fig. 2.3 (b),  $\tan \phi_0 = \frac{I_{inj}}{I_{tank}}$ ,  $I_{tank} = \sqrt{I_{osc}^2 - I_{inj}^2}$ . The lock range is

$$\omega_L = \left(\omega_0 - \omega_{inj}\right) = \frac{\omega_0}{2Q} \frac{I_{inj}}{I_{osc}} \frac{1}{\sqrt{1 - \frac{I_{inj}^2}{I_{osc}^2}}}$$

(2.17)

Where, Q means Quality factor of LC-tank. We denote this maximum difference by  $\omega_L$ , with the understanding that the overall lock range is in fact  $\pm \omega_L$  around  $\omega_0$ . The lock range is proportional to the strength of injection current  $I_{inj}$  but inversely proportional to the Q-factor of LC tank. Hence, in the design of injection locked LC oscillator, to use High-Q LC tank decrease not only required current for free-runnnig, but also lock range. Note that  $\omega_L$  is a function of Q,  $\omega_0$ , |Iosc|, and |Iinj|. Since the values of Q,  $\omega_0$ , and |Iosc| are given by design, these values experience only a little change during operation, which is caused by the variations in the supply voltage and ambient temperature. In contrast, |Iinj| can vary significantly and results in large variations of  $\omega_L$ , as the amplitude of the received input signal changes. The lock range  $\omega_L$  increases as the injection signal Iinj becomes stronger.

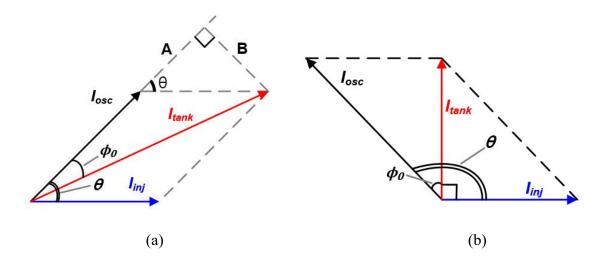

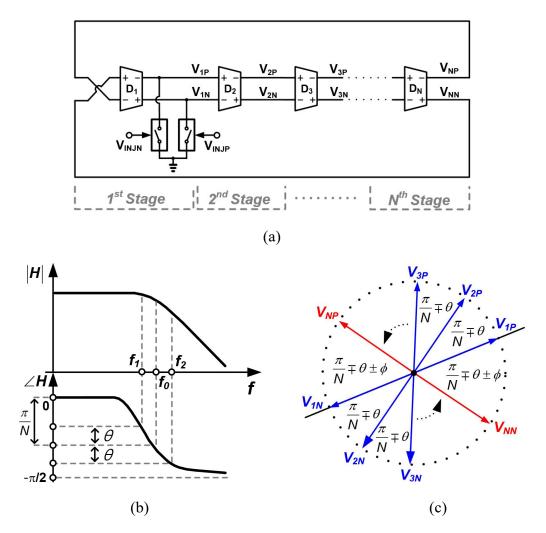

#### 2.1.2 Injection Locked Ring Oscillator

In this section, we discuss the detailed operation of the injection locked ring oscillator (ILRO), and in particular, the transient response of the injection locking process depending on whether the injection signal is higher or lower than the free-running frequency of the VCO. Primarily, the ILRO comprises a chain of interconnected delay cells as shown in Fig. 2.4 (a). Fig. 2.4 (a) shows a simplified linear model of the ring oscillator, which we have utilized for our mathematical analysis. The NMOS switch with the input  $V_{INJN}$  pulls down  $V_{IP}$  to GND when  $V_{INJN}$  is high. Given that  $V_{INJN}$  and  $V_{INJP}$  are complimentary to each other,  $V_{IN}$  remains floating as the  $V_{INJP}$  switch gets turned off. However, since  $V_{IP}$

Figure 2.4 *N*-stage injection locked ring oscillator (a) frequency response of the delay cell (b) and a phase diagram for injection locking (c).

and  $V_{IN}$  are interconnected by a latch,  $V_{IN}$  is pulled high. The overall effect of the nodes  $V_{IP}$  and  $V_{IN}$  being pulled down and up is that the phase-delay contribution of the individual delay stages changes in response to the relative frequency of the injection signal to that of the free-running frequency, taking the ILRO to be locked to a frequency equivalent as that of the injection signal. To explain this, we consider the phase response of an individual delay stage when the ILRO is free-running and also when it is injection locked.

A delay cell in the *N*-stage ILRO can be modeled as a single pole amplifier, whose amplitude response rolls off at -20 dB/dec after the dominant pole and the phase difference

between the input and output reaches  $-\pi/2$  radians at frequencies significantly higher the dominant pole as shown by the frequency response in Fig. 2.4 (b). In the ILRO, for the oscillation to sustain, the total phase shift of the loop must be a multiple of  $2\pi$  so as to meet the Barkhausen criteria [12]. To meet this, an ILRO having even number of stages, has to cross couple the inputs to one of the stages from the previous stage's outputs. In this implementation 4th delay-cell inputs are cross coupled to 3rd delay-cell outputs. In the absence of an injection signal, each non-cross-coupled delay cells of the ILRO adds a phase of  $(\pi + \pi/N)$ , while the cross coupled delay cell adds a phase of  $\pi/N$  making sure that the Barkhausen criteria is met. Note, that this phase delay responses are valid only for ILROs with even number of stages. A given delay-cell introduces an intrinsic phase reversal equivalent to  $\pi$  radians to its input signal. In addition, a variable component equal to  $\pi/N$  that depends on the number of delay stages is also added. Note that the cross-coupled stage does not add the intrinsic phase reversal to its input. Since the intrinsic phase reversal of the delay remains constant irrespective of whether the injection signal is present, it can be omitted from the rest of the analysis and is not included in the frequency response shown in Fig. 2.4 (a). The effect of injection locking is that the variable phase-delay of each of the delay cells changes in response to the injection signal to move the ILRO frequency to a locked state. It can be shown that once the ILRO is locked to the injection frequencies of  $f_0 \mp \Delta f(f_1 \text{ and } f_2)$ , the phase shift of the delay cell changes to  $\pi/N \mp \theta$ . The overall phase-shift can be expressed as:

$$\begin{cases} (N-1)\pi + N\left(\frac{\pi}{N} - \theta\right) + \phi = 2m\pi, & for \quad f_{INJ} < f_0 \\ (N-1)\pi + N\left(\frac{\pi}{N} + \theta\right) - \phi = 2m\pi, & for \quad f_{INJ} > f_0 \end{cases}$$

(2.18)

where,  $\theta$  represents the amount of phase shift caused by the change in oscillation frequency as shown by the frequency response of the delay cell (Fig. 2.4 (a)), and  $\phi$  represents the

additional amount of phase shift generated by first delay cell due to the signal injection. The factor  $(N-I)\pi$  is the sum of the intrinsic phase-shift introduced by all the delay cells in the ILRO and remains a constant. However, when injection locking occurs at a different frequency from the free-running frequency, for satisfying (2.18), the value of  $\mp N\theta$  must be canceled by  $\pm \phi$  so that the overall phase shift of the oscillator loop becomes  $2m\pi$  (m=1, 2...) to maintain oscillation at the input injection frequency. As shown in Fig. 2.4 (b), therefore, the phase shift of delay cell  $D_1$ ,  $\zeta'$ , and the phase shift of other delay cells,  $\zeta$ , when  $f_{INJ}$  is less than  $f_0$ , can be described as follows:

$$\begin{cases}

\zeta = \frac{\pi}{N} - \theta, \\

\zeta' = \frac{\pi}{N} - \theta + \phi = \frac{\pi}{N} - \theta + N\theta

\end{cases} (2.19)$$

Similarly, the phase shift of delay cell  $D_1$ ,  $\psi'$ , and the phase shift of other delay cells,  $\psi$ , when  $f_{INJ}$  is greater than  $f_0$ , can be described as follows:

$$\begin{cases} \psi = \frac{\pi}{N} + \theta, \\ \psi' = \frac{\pi}{N} + \theta - \phi = \frac{\pi}{N} + \theta - N\theta \end{cases}$$

(2.20)

For find out value of  $\theta$ , we consider the schematic of ILRO as shown in Fig. 2.4 (a). Let's assume that the model comprises equivalent output resistance (R) and load capacitance (C) for each delay cell stage. The linear model yields a first-order transfer function for each stage expressed as:

$$H(f) = \frac{-A}{1 + j\frac{f}{f_0}} \tag{2.21}$$

Where, A is the gain of single stage delay cell, and  $f_0$  can be calculated by

$$f_0 = \frac{1}{2\pi RC} \tag{2.22}$$

The ILRO can oscillate at  $f_{osc}$  since each stage should contribute  $\pi/N$  phase shift.

$$tan^{-1}\frac{f_{osc}}{f_0} = \frac{\pi}{N} \tag{2.23}$$

$$f_0 = \frac{1}{\tan(\frac{\pi}{N})} \cdot f_{osc} \tag{2.24}$$

where,  $f_{osc}$  is the free-running frequency of the ring oscillator. Consequently, open-loop transfer function for each stage of ring oscillator is:

$$H(f) = \frac{-A}{1+j\tan(\frac{\pi}{N})(\frac{f}{f_{OSC}})}$$

(2.25)

In the free-running state, f is equals to  $f_{osc}$  in equation. The phase shift of the one stage in the ring oscillator is  $\pi/N$ . But in injection locking state,  $f_{osc}$  moves to  $f_{inj} = f_{osc} \pm \Delta f$ . The phase shift of the one stage in the ring oscillator can be represented as:

$$\tan\left(\frac{\pi}{N} \pm \theta\right) = \tan\left(\frac{\pi}{N}\right) \left(\frac{f_{inj}}{f_{osc}}\right) \tag{2.26}$$

Hence,  $\theta$  according to the oscillation frequency in the lock state can be expressed as [13]:

$$\theta = \left| \tan^{-1} \left[ \tan \left( \frac{\pi}{N} \right) \frac{f_{INJ}}{f_0} \right] - \frac{\pi}{N} \right| \tag{2.27}$$

As a result, the phase shift of delay cell is changed from  $\pi/N$  according to the injection signal frequency.

## 2.2 Conversion Process of Injection Locked Oscillator

### 2.2.1 Conversion of OOK Signal

Figure 2.5 Phasor diagrams of ILO currents for the OOK-modulated injection signal when: (a)  $I_{inj}$  is on and (b)  $I_{inj}$  is off.

Fig. 2.5 shows how the amplitude variations of the OOK-modulated input signal are preserved at the ILO output. When  $I_{inj}$  is on to present the data bit of '1', the  $I_{inj}$  is added to the  $I_{osc}$  to produce  $I_{tank}$ , and hence the amplitude of  $I_{tank}$  (=  $|I_{tank,a}|$ ) becomes larger than that of  $I_{osc}$ :

$$|I_{tank,a}| = \sqrt{|I_{osc}|^2 + |I_{inj}|^2 + 2|I_{osc}||I_{inj}|\cos\theta_a}$$

(2.28)

On the other hand, if  $I_{inj}$  is off to present the data bit of '0', the amplitude of  $I_{tank}$  (=  $|I_{tank,b}|$ ) becomes the same as that of  $I_{osc}$ :

$$\left|I_{tank,b}\right| = \left|I_{osc}\right| \tag{2.29}$$

Multiplied by  $Z_{tank}$ , the  $I_{tank}$  generates the amplitude-modulated  $V_{out}$  signal.

In conclusion, the OOK input signal is also processed by the ILO to generate the amplitude-modulated signal at the output, as in the cases of BFSK and DBPSK input signal. Based on this conversion process of the ILO, an energy-efficient receiver IC can be constructed. The implementation details of the receiver circuits are described in the next section.

### 2.2.2 Conversion of BFSK Signal

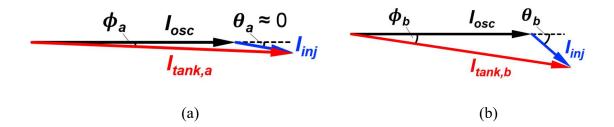

Figure 2.6 Phasor diagrams of injection locked LC oscillator currents for the FSK-modulated injection signal when: (a)  $\omega_{inj} = \omega_a \approx \omega_0$  and (b)  $\omega_{inj} = \omega_b = \omega_a + \Delta \omega$ .

Assume that the injection frequency  $\omega_a$  representing the data bit of '1' is set close to the self-resonance frequency  $\omega_0$  and hence  $\theta_a \approx 0$  as depicted in Fig. 2.6 (a). Then, from (1), the  $|I_{tank,a}|$  can be approximated as

$$|I_{tank,a}| = \sqrt{|I_{osc}|^2 + |I_{inj}|^2 + 2|I_{osc}||I_{inj}|\cos\theta_a} = |I_{osc}| + |I_{inj}|$$

(2.30)

The output voltage amplitude of the ILO corresponding to '1' (=  $|V_{out,a}|$ ) is produced by the multiplication of  $|I_{tank,a}|$  and  $|Z_{tank}(\omega_a)|$  ( $\approx |Z_{tank}(\omega_0)|$ ). Since  $|I_{tank,a}|$  and  $|Z_{tank}(\omega_a)|$  are close to the maximum possible values of  $|I_{tank}|$  and  $|Z_{tank}|$  respectively,  $V_{out,a}$  presents nearly the largest output swing.

On the other hand, if the injection frequency  $\omega_b = \omega_a + \Delta \omega$  used to indicate the data bit of '0' is set far from  $\omega_0$  but within the lock range, as shown in Fig. 2.6 (b), the  $|I_{tank,b}|$  is given by

$$|I_{tank,b}| = \sqrt{|I_{osc}|^2 + |I_{inj}|^2 + 2|I_{osc}||I_{inj}|\cos\theta_b}$$

(2.31)

The output voltage amplitude of the ILO corresponding to '0' (=  $|V_{out,b}|$ ) is derived by multiplying  $|I_{tank,b}|$  with  $|Z_{tank}(\omega_b)|$  ( $< |Z_{tank}(\omega_0)|$ ). Since  $|I_{tank,b}|$  and  $|Z_{tank}(\omega_b)|$  are smaller than

$|I_{tank,a}|$  and  $|Z_{tank}(\omega_a)|$  respectively,  $|V_{out,b}|$  is also smaller than  $|V_{out,a}|$ . How large amplitude difference between  $V_{out,a}$  and  $V_{out,b}$  is obtained for the frequency deviation of  $\Delta \omega = |\omega_b - \omega_a|$  determines the frequency-to-amplitude conversion ratio.

Note that once the injection frequency  $\omega_b$  for the data bit of '0' is determined, the corresponding phase shift  $\phi_b$  is fixed as described in Fig. 2.1 (b). It can be found in Fig. 2.6 (b) that, for the same  $\phi_b$ , if  $|I_{inj}|$  increases,  $\theta_b$  decreases, and hence  $\cos \theta_b$  approaches 1. In other words, the difference between  $|I_{tank,a}|$  and  $|I_{tank,b}|$  becomes smaller, and thus the frequency-to-amplitude conversion ratio decreases as  $|I_{inj}|$  increases. It demonstrates the need for prohibiting any significant variations in the magnitude of  $I_{inj}$  to obtain a consistent demodulation performance over a wide range of received RF signal strength.

To achieve a good sensitivity, the receiver should be designed to operate even with a very weak RF input signal, which leads to a very small amplitude of  $I_{inj}$ . Since  $\omega_L$  is narrow for small  $|I_{inj}|$  as predicted by (7), the  $\omega_a$  and  $\omega_b$  cannot be separated too far from each other. The ILO-based receiver is therefore designed to generate a distinguishable amplitude change for such a small frequency difference when  $|I_{inj}|$  is small. However, if a strong RF signal is received and hence the amplitude of  $I_{inj}$  increases, the  $\omega_L$  becomes wide, and the frequency-to-amplitude conversion ratio reduces significantly, resulting in too small amplitude change at the ILO output to be discriminated properly. To avoid this problem, it is important to control the magnitude of  $I_{inj}$  to stay relatively constant.

### 2.2.3 Conversion of DPSK Signal

The conversion process from the DBPSK-modulated signal to the amplitude-modulated signal by the ILO is depicted in Fig. 2.7. Since  $I_{tank}$  is the vector sum of  $I_{osc}$  and  $I_{inj}$ , and  $V_{out}$

Figure 2.7 Phasor diagrams of injection locked LC oscillator currents for the PSK-modulated injection signal when: (a) (a)  $\theta_{inj} = \theta_0$  and (b)  $\theta_{inj} = \theta_0 + \pi$ .

is the multiplication of  $I_{tank}$  and  $Z_{tank}$  when there is a phase change of  $\pi$  in  $I_{inj}$ , the amplitude of  $V_{out}$  changes accordingly [14].

When the ILO is in the injection-locked state, and  $I_{inj}$  forms the angle of  $\theta_a$  with respect to the  $I_{osc}$  to represent the data bit of '1',  $|I_{tank,a}|$  is given by

$$|I_{tank,a}| = \sqrt{|I_{osc}|^2 + |I_{inj}|^2 + 2|I_{osc}||I_{inj}|\cos\theta_a}$$

(2.32)

as described in Fig. 2.7 (a).

If the angle between  $I_{inj}$  and  $I_{osc}$  changes to  $\theta_b = \theta_a + \pi$  which corresponds to the data bit of '0', the ILO is perturbed from its injection-locked state and the magnitude of  $I_{tank}$  experiences an instantaneous change to  $|I_{tank,b}|$ , which is expressed as

$$|I_{tank,b}| = \sqrt{|I_{osc}|^2 + |I_{inj}|^2 + 2|I_{osc}||I_{inj}|\cos(\theta_a + \pi)}$$

$$= \sqrt{|I_{osc}|^2 + |I_{inj}|^2 + 2|I_{osc}||I_{inj}|\cos\theta_a}$$

(2.33)

After this transient change, as the frequency of the injection signal does not change, the ILO returns to the injection-locked state, as shown in Fig. 2.7 (a) and the magnitude of  $I_{tank}$  settles back to  $|I_{tank,a}|$ . In other words, the output amplitude of ILO fluctuates when the phase of the injection signal changes abruptly.

As a result, the output amplitude of ILO fluctuates when the phase of the injection signal changes abruptly, and this amplitude variation can be captured by the following ED circuit, obviating the need for power-hungry circuit blocks such as the frequency synthesizer and mixer. Note that the output of the ED behaves like an RZ signal, which requires a conversion to the NRZ signal for input data recovery [14].

### 2.2.4 Frequency to Phase Conversion

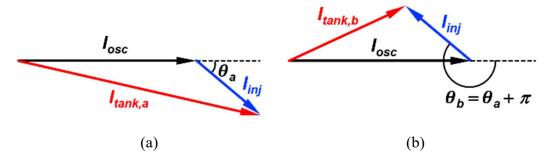

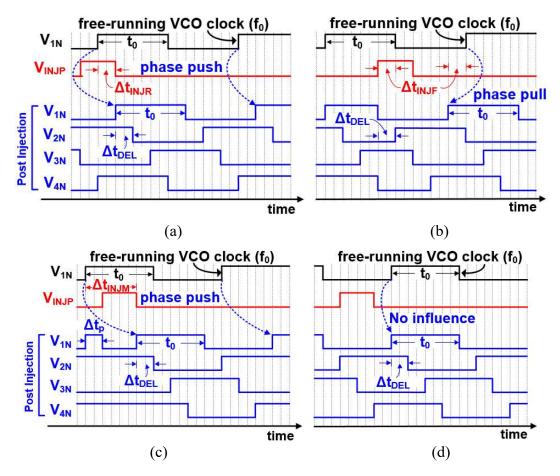

To understand the concept of the injection locking process in the ILRO, we can consider the transient response of the output nodes of each of the ILRO delay cells. Several possible scenarios that show the relative alignment of an injection signal to the free-running VCO clock frequency ( $f_0$ ) and how it modifies the phase-response of the ILRO clock outputs are shown Fig. 2.8. The illustration only shows the effect of a single injection signal pulse. As discussed earlier, in the absence of an injection signal, each of the delay cells introduce a variable phase-delay equivalent to  $\pi/N$ . We assume that the equivalent time-delay corresponding to a phase-delay of  $\pi/N$  is represented by  $\Delta t_{DEL}$ . The effect of the injection signals  $V_{INJP}$  or  $V_{INJN}$  are that it pulls down the nodes  $V_{IN}$  or  $V_{IP}$  to GND when one of them goes high. If either  $V_{IN}$  or  $V_{IP}$  are already at the GND level, the injection signal does not alter that node at all. Thus, the injection signal can affect the ILRO when both  $V_{IN}$  and  $V_{INJP}$  are high or when  $V_{IP}$  and  $V_{INJN}$  are high. The relative alignment of the injection signal and the free-running clock pulse can be summarized into four different scenarios:

Scenario 1: The injection pulse  $V_{INJP}$  overlapping the rising edge of the free-run- ning clock  $V_{IN}$  as shown in Fig. 2.8 (a). The overlap interval between  $V_{INJP}$  and  $V_{IN}$  is denoted as  $\Delta t_{INJR}$ .

Figure 2.8 Change of 4-stage ILRO output according to injection position rising edge (a), falling edge (b), high state (c) and low state (d).

- Scenario 2:  $V_{INJP}$  overlapping the falling edge of the  $V_{IN}$  as shown in Fig. 2.8 (b). The overlap interval in this case is denoted as  $\Delta t_{INJF}$ .

- Scenario 3:  $V_{INJP}$  overlapping the high-state of  $V_{IN}$  as shown in Fig. 2.8 (c), where the time-interval between the rising edge of  $V_{IN}$  and the falling edge of the injection signal is  $\Delta t_{INJM}$ .

- Scenario 4:  $V_{INJP}$  overlapping the low-state of  $V_{IN}$  as shown in Fig. 2.8 (d). When the injection signal  $V_{INJP}$  overlaps the rising edge of the free-running signal  $V_{IN}$ , (Fig. 2.8 (a)), the low state of the  $V_{IN}$ , is retained for an additional  $\Delta t_{INJR}$  time. The result of this is that the  $V_{IN}$  pulse is delayed by  $\Delta t_{INJR}$ . In contrast, when  $V_{INJP}$  overlaps the falling

edge of  $V_{IN}$ , (Fig. 2.8 (b)), the injection signal pulls down  $V_{IN}$  earlier by  $\Delta t_{INJF}$ , causing the  $V_{IN}$  to advance by the same time-interval. When  $V_{INJP}$  overlaps with the high-state of  $V_{IN}$ , (Fig. 2.8 (c)), the effect on  $V_{IN}$  is similar to that of the case shown in Fig. 2.8 (a), where the rising edge is delayed. However, in this case, the delay time is equivalent to the time-interval between the rising edge of  $V_{IN}$  and the falling edge of the injection signal,  $\Delta t_{INJM}$ . Effectively, this scenario operation causes a glitch in the  $V_{IN}$  waveform, whose width is shown as  $\Delta t_P$ . If  $\Delta t_P$  is lower than the default delay time of the subsequent stages, it will not affect them as shown in Fig. 2.8 (c). However, if  $\Delta t_P$  is larger, this glitch would manifest in  $V_{2N}$ ,  $V_{3N}$  and also  $V_{4N}$ . Irrespective of the magnitude of  $\Delta t_P$ , the fact that the rising edge would be delayed remains the same. Finally, the  $V_{INJP}$  has no effect on  $V_{IN}$  when it overlaps with its low-state as shown in Fig. 2.8 (d). In a practical operating scenario, a sequence of the above four cases lead the ILRO to be locked to a frequency equal to the injection signal.

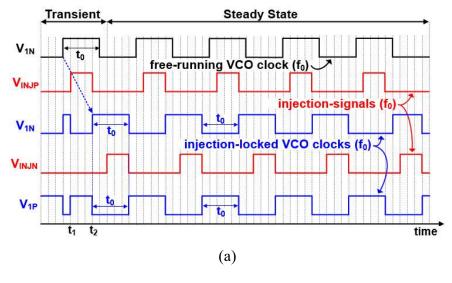

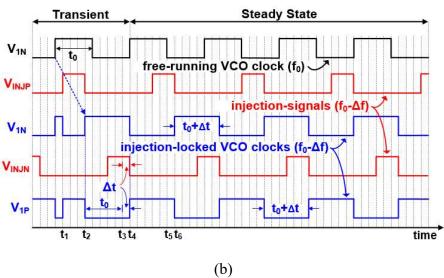

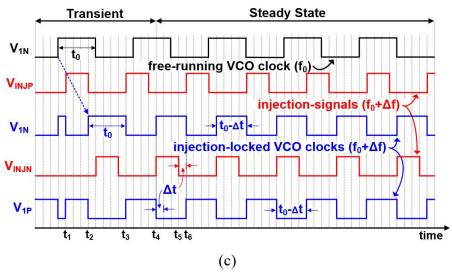

To illustrate the locking mechanism further, the transition process from a free-running state to a locked state when the injection signal is applied to the middle of high state of free-running signal (shown in Fig. 2.8 (c)), is shown in Fig. 2.9. In practice, the relative alignment of the injection signal could possibly be any one of the scenarios mentioned in Fig. 2.8. However, this scenario is chosen for illustration as it involves the events shown in the other cases of Fig. 2.8 as will be discussed later.

The transient operation is discussed for cases when the injection signal frequency is equal to, lower and higher than the free-running frequency of the ILRO. Fig. 2.9 (a) shows the transient operation when the frequency of  $V_{INJP}$  is equal to the free-running frequency of the ILRO,  $V_{IN}$ . The  $V_{INJP}$  signal resets the node voltage  $V_{IN}$  to GND at the instant  $t_1$ . As the  $V_{INJP}$  goes low, the  $V_{IN}$  node rises to a high-state at  $t_2$ , thereby delaying the rising edge of

Figure 2.9 Injection-locking transient responses at  $f_{INJ} = f_0$  (a),  $f_{INJ} < f_0$  (b) and  $f_{INJ} > f_0$  (c).

the free-running VCO clock. This is the scenario 3 of the locking process. Thereafter, the  $V_{INJP}$  or the  $V_{INJN}$  signals will not affect the ILRO operation, as they would overlap with the low-state of the  $V_{IN}$  and  $V_{IP}$ , which is the scenario 4 of the locking process. Thus, despite the phase-push introduced by  $V_{INJP}$  and  $V_{INJN}$ , the ILRO frequency remains the same. Fig. 2.9 (b) shows the transient operation when the frequency of  $V_{INJP}$  is lower than the free-running frequency the ILRO,  $V_{IN}$ . At the instant  $t_1$ , the  $V_{INJP}$  goes high, pulling down the  $V_{IN}$  to GND. At t<sub>2</sub>, the  $V_{INJP}$  goes low, leaving  $V_{IN}$  floating. As a result, the rising edge of  $V_{IN}$  is delayed to the instant  $t_2$ , causing a phase-push (scenario 3). In the absence of the injection signal at  $V_{INJN}$ , the  $V_{IP}$  should have gone to a high-state at the instant  $t_3$ . However, as  $V_{IP}$  is pulled down by  $V_{INJN}$  until, t<sub>4</sub> the signal  $V_{IP}$  stays low for an extended period of  $\Delta t$ , thereby locking the ILRO to the lower injection frequency (scenario 1). Between  $t_5$  and  $t_6$ , the  $V_{INJP}$  holds  $V_{IN}$  down to GND for an additional  $\Delta t$  (scenario 1). Once a lock is achieved, the scenario 1 repeats alternatively in  $V_{IN}$  and  $V_{IP}$ . When the injection signal frequency is higher than the free running frequency of the ILRO (Fig. 2.9 (c)), a phase-push happens and delays the rising edge of the  $V_{IN}$  to  $t_2$  (scenario 3). Between  $t_2$  and  $t_4$ ,  $V_{INJN}$  and  $V_{INJP}$  go high without influencing the current state of  $V_{IP}$  and  $V_{IN}$  respectively as they are already at GND (scenario 4). However, at t<sub>4</sub>,  $V_{INJN}$  pulls down  $V_{IP}$  to GND, causing the  $V_{IN}$  to rise to a high-state instantaneously (scenario 2). The overall effect of this is that the period is reduced by  $\Delta t$ , thereby locking the ILRO to the injection frequency that is higher than the free-running frequency. Once locked, the scenario 2 repeats alternatively in  $V_{IN}$  and  $V_{IP}$ .

In summary, the complimentary injection signals  $V_{INJP}$  and  $V_{INJN}$  introduces a phase-push/pull along with the widening or shortening of the ILRO outputs leading it to be locked with a frequency lower or higher than the nominal ILRO operating frequency.

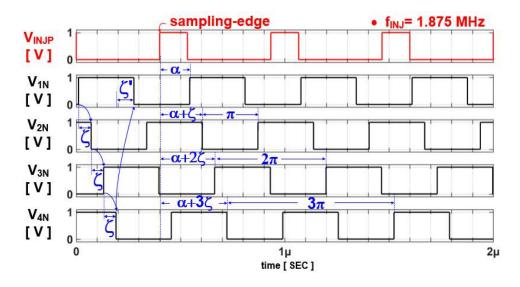

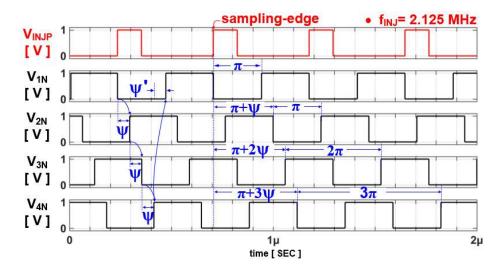

Figure 2.10 Phase-relationships with the sampling edge at  $f_{INJ} < f_0$  (a) and  $f_{INJ} > f_0$  (b).

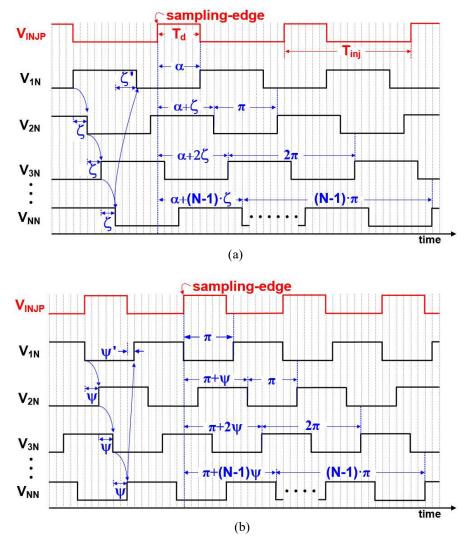

Fig. 2.10 shows the output waveform of each node of N-stage ILRO in the steady state after injection locking. When the ILRO is locked to an injection signal frequency that was originally lower its free-running frequency as shown Fig. 2.10 (a), the phase-delay between the successive edges between  $V_{NN}$  and  $V_{IN}$  becomes equal to  $\zeta' = \pi/N - \theta + \phi$  as shown by equation (2.19). However, the delay between the successive edges of the other stages such as between  $V_{IN}$  and  $V_{2N}$ ,  $V_{2N}$  and  $V_{3N}$  and so on remains at  $\zeta = \pi/N - \theta$ . The output is obtained by sampling one of the ILRO outputs using the injection locking clock. The fixed relative-

Table 2.1 Sapling State According to the Phase Difference

| Output Stage | $f_{INJ} < f_0 \text{ or } f_{INJ} > f_0$ |      |

|--------------|-------------------------------------------|------|

| Even         | $PD_k > k\pi$                             | Low  |

|              | $PD_k < k\pi$                             | High |

| Odd          | $PD_k > k\pi$                             | High |

|              | $PD_k < k\pi$                             | Low  |

phase relationship between the injection signal and the locked ILRO outputs enable latching one of the outputs at the sampling edge such that the output is registered as logic-high or logic-low. To explain this and to develop a closed form expression, the phase difference (PD) between the sampling edge of the input signal  $V_{INJP}$  and the successive rising edges of ILRO delay cell outputs  $V_{kN}$  can obtained as follows:

$$PD_k = \alpha + (k-1) \cdot \left(\pi + \frac{\pi}{N} - \theta\right) \quad for \quad f_{INJ} < f_0$$

(2.34)

where k denotes the index of the stage from which the output is taken. In (2.34),  $\alpha$  denotes a phase equivalent to a duty-cycle of  $T_d \times 2\pi / T_{inj}$ . Similar to this, a definite phase-relationship exists between  $V_{INJP}$  and  $V_{NN}$ , when the injection signal frequency is higher than the free-running ILRO frequency as shown in Fig. 2.10 (b). The phase-delay between the successive edges between  $V_{NN}$  and  $V_{IN}$  becomes equal to  $\psi' = \pi/N + \theta - \phi$  from equation (2.20). However, the delay between the successive edges of the other stages such as between  $V_{IN}$  and  $V_{2N}$ ,  $V_{2N}$  and  $V_{3N}$  and so on becomes at  $\psi = \pi/N + \theta$ . In this case, however, the PD between the sampling edge of the input signal  $V_{INJP}$  and the successive rising edges of ILRO delay cell of outputs  $V_{kN}$  can be shown as:

$$PD_k = \pi + (k-1) \cdot \left(\pi + \frac{\pi}{N} + \theta\right) \qquad for \quad f_{INJ} > f_0$$

(2.35)

Using the relationships (2.34) and (2.35), an appropriate ILRO output can be sampled as the demodulator output as shown in Table 2.1. Due to the injection locking, a well-defined phase-relationship is established between  $V_{INJP}$  and the ILRO outputs  $V_{kN}$  and  $V_{kP}$ , where k refers to the state from which the outputs are taken. As shown in Table I, for an even stage, (k=2, 4...) if the total phase difference between the sampling edge and the rising edge of k<sup>th</sup> delay cell output is greater than  $k\pi$ , the output will be sampled as active high. If the outputs are taken from the odd numbered stages (k=1, 3...) and the overall phase difference between the sampling edge and the rising edge of k<sup>th</sup> delay cell output is higher than  $k\pi$ , the output will be sampled as active high. If the phase difference is lower than  $k\pi$ , the output will be sampled as active low.

Finally, as observed from (2.34) and (2.35), the sampled output state in the cases when  $f_{INJ}$  is greater or lower than  $f_0$  depends on the duty-cycle of injection signal. As shown in Table I and using N=4 and k=2 (values used by this design as discussed later), the DFF samples the low-state when the duty-cycle is over 38 % and the high-state when the duty-cycle is less than 38 % when  $f_{INJ}$  is lower than  $f_0$ . However, when  $f_{INJ}$  is higher than  $f_0$ , the DFF is always sampled as a logic-low as shown by (2.35) and Table 2.1. Therefore, in this thesis, a duty-cycle of 25 % is used so as to provide a margin of 13 % from the maximum

### 2.3 Summary

The operation principle of the injection locked LC oscillator and ring oscillator investigated in this chapter. An injection locked LC oscillator can translates the signal modulated with various modulation schemes such as OOK, BFSK, and DBPSK into a simple amplitude-modulated signal in the lock range. Using these characteristics of injection locked oscillator, an energy-efficient injection locked LC oscillator based receiver supporting multi-mode can be implemented. Because, injection locked LC oscillator allows to use simple envelope detection circuit for frequency down-conversion and signal demodulation. The implementation details of the receiver circuits are described in the next chapter. Furthermore, an injection locked ring oscillator can convert frequency to phase difference. Using this property, simple and ultra-low power FSK demodulator can be implemented. The details of the demodulator circuits are described in chapter IV.

# III. Multi-Mode Receiver Based on an Injection

# **Locked LC Oscillator**

### 3.1 Overall Receiver Architecture

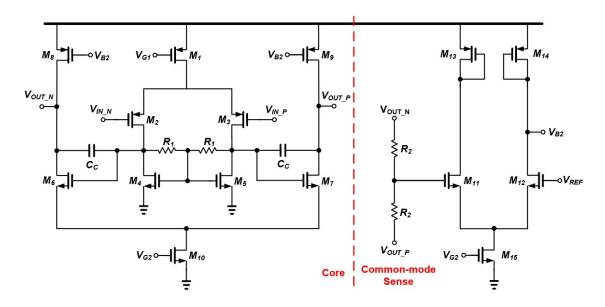

Figure 3.1 Overall architecture of the proposed wireless receiver system.

Fig. 3.1 is the block diagram showing the overall architecture of the proposed wireless receiver system, consisting of the front-end matching network, RF receiver IC, and microcontroller unit (MCU). In the RF receiver IC, the ILO converts the received OOK/BFSK/DBPSK signal to the amplitude-modulated signal. Based on such ILO operation, an energy-efficient wireless receiver can be realized by employing an envelope detector (ED) for RF-to-baseband frequency down-conversion and demodulation. The external MCU generates a gain control signal for the SDA based on the output amplitude of the baseband amplifier (BB AMP), which is measured by the peak detector. Through this closed-loop control, the magnitude of the RF signal injected to the ILO can be kept fairly

constant, and hence a significant change in the frequency-to-amplitude conversion ratio of the ILO can be prohibited when the BFSK signal is received.

The RF signal received by the antenna is fed to the preamplifier (Pre-AMP) through the matching network. The Pre-AMP amplifies the RF signal with moderate gain and provides isolation between the matching network and the SDA input to relieve the requirement of input-impedance matching for the SDA.