# Vacuum Tunneling Transistor with Nano Vacuum Chamber for Harsh Environments

Su Jin Heo, Jeong Hee Shin, Byoung Ok Jun, and Jae Eun Jang\*

Cite This: ACS Nano 2023, 17, 19696-19708

**ACCESS**

Metrics & More

Article Recommendations

Supporting Information

ABSTRACT: A nano vacuum tube which consists of a vacuum transistor and a nano vacuum chamber was demonstrated. For the device, a vacuum region is an electron transport channel, and a vacuum is a tunneling barrier. Tilted angle evaporation was studied for the formation of the nano level vacuum chamber structure. This vacuum tube was ultraminiaturized with several tens of 10<sup>-18</sup> L scale volume and 10<sup>-6</sup> Torr of pressure. The device structure made it possible to achieve a high integration density and to sustain the vacuum state in various real operations. In particular, the vacuum transistor performed stably in extreme external environments because the tunneling mechanism showed a wide range of working stability. The vacuum was sustained well by the sealing layer and provided a defect-free tunneling junction. In tests, the high vacuum level was maintained for more than 15 months with high reliability. The Al sealing layer and tube structure can effectively block exposed light such as visible light and UV, enabling the stable

operation of the tunneling transistor. In addition, it is estimated that the structure blocks approximately 5 keV of X-ray. The device showed stable operating characteristics in a wide temperature range of 100-390 K. Therefore, the vacuum tube can be used in a wide range of applications involving integrated circuits while resolving the disadvantages of a large volume in old vacuum tubes. Additionally, it can be an important solution for next-generation devices in various fields such as aerospace, artificial intelligence, and THz applications.

KEYWORDS: nano vacuum tube, vacuum tunneling, nano vacuum chamber, tilted angle deposition, extreme environment stability

ith advances in existing electronic devices and the appearance of innovative devices, extreme performance is required. The importance of developing devices that have high integration and miniaturization, high performance, high efficiency, and high operating speed has thus increased. 1-3 In addition, with the electrification of conventional machinery such as electric vehicles and the change of working environments, reliable operation is necessary for highly challenging environments, especially including the harsh environmental conditions of space such as extreme temperatures, ultraviolet (UV) exposure, X-ray, and radiation. <sup>1,4-6</sup>

Device operating mechanisms and designs should be considered to withstand these extreme conditions. Quantum mechanical tunneling is a good candidate solution.<sup>7,8</sup> A tunneling device has an ultrathin potential barrier so that electrons can penetrate the potential barrier. Thus, it can show high operating speed, a sub-60 mV/decade subthreshold swing, low operating voltage, and high current efficiency. 9-11 Usually, an oxide material or a semiconductor is used as the tunneling barrier. 12-17 However, in this case, some issues still remain, such as electron trap and scattering due to the defects in the barrier. This easily degrades the electrical properties of

Old vacuum tube technology can point toward a direction to resolve these issues.<sup>3,18</sup> A vacuum is one of the ideal tunneling barriers, and it is almost free from defects. Due to the absence of trap sites and electron interference in the ideal vacuum, the vacuum device exhibits ballistic transport properties. 4,6,19 Therefore, the vacuum device can have high-speed switching with high stability. 20,21 Additionally, a vacuum tunneling device can be more robust in harsh environmental conditions such as a wide driving temperature or radiation conditions due to the empty channel.<sup>5,22,23</sup> In the past, vacuum tubes were dominantly used as a key component of electronic circuits. 24-26 However, despite these advantages, the old vacuum tubes have some limitations. They are difficult to use in large-scale integrated circuits due to the large sealing

Received: March 31, 2023 Accepted: October 4, 2023 Published: October 6, 2023

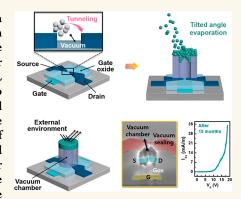

Figure 1. (a) Theoretical electron mean free path according to the pressure. (b) Schematic of tilted angle evaporation. (c) Schematics of vacuum tunneling transistor without a vacuum tube (left) and with a vacuum tube (right). (d) Fabrication process of vacuum tunneling transistor with nano vacuum chamber.

volume and poor durability of glass sealing and consequently were replaced by semiconductor devices and integrated circuit (IC) design. To use vacuum technology with recent advanced technology, miniaturized sealing technology should be developed.

The operation of recent vacuum devices follows the field emission by Fowler–Nordheim (FN) tunneling. <sup>12,27–32</sup> The high electric field is applied at the electrode; the electrons can be emitted into the vacuum region, and they are attracted to

the opposite electrode due to the applied bias. Especially, in the transistor structure, the potential barrier becomes sharper due to the applied gate field. 5,6,25,33,34 Therefore, the electrons easily penetrated and were emitted into the vacuum. Some research groups studied various vacuum sealing methods to operate vacuum devices under general conditions. These techniques are based on a microelectronic mechanical systems (MEMS) structure. However, this fabrication process is complicated and requires many fabrication steps. Moreover,

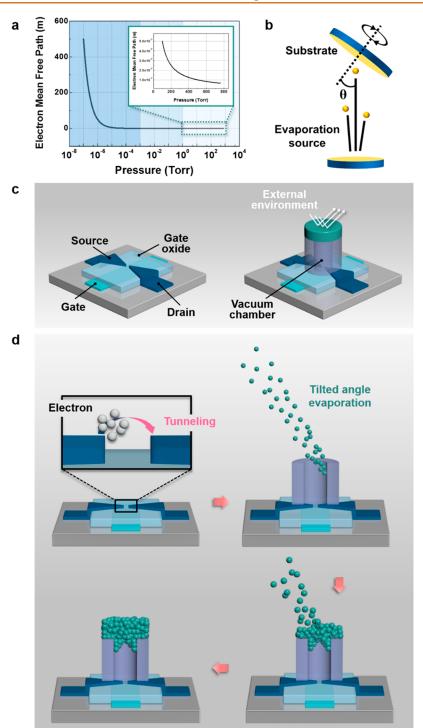

Figure 2. Tilted angle simulation using Python according to the tilted angle and aspect ratio: (a) aspect ratio 1; (b) aspect ratio 1.5; (c) aspect ratios 0.5, 2, 1 and tilted angles 45°, 45°, 20°, respectively. (d) Relationship among aspect ratio, tilted angle, and height. (e) Height value according to the tilted angle at each aspect ratio.

the sealing size level is still at the micrometer level or even a millimeter scale. Recently, emerging materials were used for vacuum enclosure such as graphene which has high transparency and ultrathin thickness. 42-44 Therefore, it is possible to pass the electric field and electrons. So, it works as an electrode (grid) and as vacuum encapsulation. However, this method is difficult to use in compatibility with complementary metal oxide semiconductor (CMOS) fabrication. As an alternative solution, other researchers fabricated a vacuum device with an ultranarrow gap that was less than the electron mean free path (MFP) in air. <sup>22</sup>,23,26 Therefore, if the tunneling gap size is less than the MFP, vacuum tunneling can be possible in air conditions. Although this is theoretically possible, a reliability issue is anticipated to impede realization and commercialization. Therefore, many groups have focused on improving the performance of tunneling devices using a large size test vacuum system, instead of finding nanometer level vacuum sealing methods for realization. 19,455

Here, we suggested and studied a nano vacuum tunneling tube structure. The vacuum chamber structure is the key component to maintain the vacuum and to stably operate the vacuum transistor in air. To minimize the electron trap and scattering issues, the vacuum sealing of the nano vacuum tube was carried out in a high vacuum state. To produce a high vacuum state with a nanometer level sealing structure, we should use a micro- or nanofabrication process. To this end, we studied tilted low angle evaporation to seal the nano cylinder chamber with a high vacuum state. Compared with old glass tube vacuum sealing technology, the evaporation sealing process is quite compatible with the fabrication process of a tunneling transistor and guarantees high integration density. The suggested vacuum transistor consists of a metalvacuum-metal junction with a bottom gate electrode. Therefore, we can develop an ultraminiaturized volume

vacuum tube and the transistor can operate in atmospheric pressure without any vacuum measurement system. It also has a long lifetime and can endure various harsh environments without significant errors or degradation.

## RESULTS AND DISCUSSION

Nano Vacuum Chamber Using Tilted Angle Evaporation. The nano vacuum tunneling tube fabricated by a specific sealing process based on the nano and micro fabrication process was studied to operate as a vacuum tunneling device and enhance its performance without any other vacuum pumping systems. The electron mean free path can be calculated by eq  $1^{49}$

$$l = \sqrt{\frac{\pi}{8}} \frac{\mu}{u} \frac{1}{\sqrt{\rho P}} \tag{1}$$

where  $\mu$  is the coefficient of viscosity of air, u is the numerical factor, P is the pressure, and  $\rho$  is the density of air. According to the equation, in ideal conditions, the electron MFP is less than ~67 nm at atmospheric pressure of 760 Torr at 300 K. We can calculate the electron MFP according to the pressure, and it increases dramatically (10-fold or more) approaching a high vacuum (Figure 1a). In high-vacuum conditions ( $\sim 10^{-6}$ Torr), the MFP is dramatically increased by over 1 m. Therefore, a higher vacuum state can guarantee the reliability and stability of the vacuum tunneling barrier, which is one of the most important structures of tunneling devices. The vacuum chamber allows us to operate the tunneling transistor in atmospheric pressure regardless of the tunneling gap. To realize a nano level vacuum chamber structure, we fabricated the vacuum chamber by a process based on tilted angle evaporation. Sometimes, this tilted angle evaporation has been applied to form various structures. One example is the Spindt-type device, one of the key device structures for vacuum

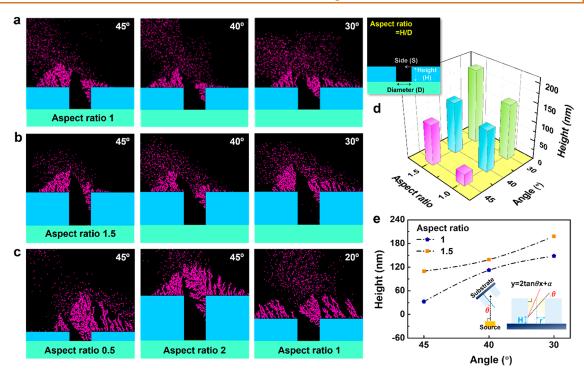

Figure 3. SEM images of the nano vacuum chamber at each step: (a) top view and (b) cross-sectional images of single and array vacuum cylinder before vacuum sealing with 300 nm hole diameter. (c) Cross-sectional image of vacuum chamber fabricated without rotation with 300 nm hole diameter and 45° tilted angle. (d) Cross-sectional images of vacuum chamber with 30° tilted angle according to the hole diameter. (e) Cross-sectional images with aspect ratio of 1 according to the tilted angle. (f) Measured top sealing layer thickness by the tilted evaporation angle. (g,h) Results of actual height (from bottom to deposition starting point) according to the hole diameter and tilted angle. (i) Calculated volumes of vacuum chamber by the hole diameter.

field emission. 50-53 The device uses this method to form a vertical sharp tip electrode for electron emission into a vacuum. 8,54-56 The tilted evaporation is used to form a very thin sacrificial layer for the lift-off process. The tilted angle evaporation has generally a poor step coverage and shadow effect, and we tried to use these in reverse for the nano vacuum sealing process. The tilted angle is between the intersection of the vertical line of the sample surface and the vertical line of the deposition source (Figure 1b). After the formation of the tunneling device, a nano cylinder structure was fabricated by a general semiconductor process, deposition, lithography, and etching. The substrate was then loaded into an evaporation system. During evaporation, a high vacuum level ( $\sim 10^{-6}$  Torr) was sustained in the process chamber by various vacuum pumping systems. Therefore, if we can cap the nano cylinder structure in the evaporation system, we can obtain a good nano vacuum chamber. The vacuum tunneling transistor was fabricated with a bottom gate structure to control the electric field in the vacuum barrier, and the nano vacuum chamber was placed between the source and drain (Figure 1c). The details can be seen in the schematic of the fabrication process of the nano vacuum tunneling tube (Figure 1d).

Before the vacuum sealing process, a simulation was carried out to estimate the paths of the evaporation particles and the deposition form. Pygame, a library for multimedia expressions that can be written in Python, was used as a simulation tool. The simulation function was based on a Gaussian distribution. In order to fabricate devices without other issues such as electrical short, cutoff, or damage, the top sealing layer should not be deposited on the bottom of the chamber where the tunneling transistor is formed. From Pythagoras' theorem, if the aspect ratio of the cylinder is 1, the tilted angle of evaporation should be at least 45° in order to avoid deposition at the bottom. At this time, the limit of the tilted angle can change depending on the aspect ratio, and the minimum aspect ratio also changes according to the tilted angle. Therefore, the aspect ratio and tilt angle were set as the simulation variables.

The aspect ratios were selected as 1 and 1.5, and the tilted angles were 30°, 40°, and 45°. The deposition angle without tilting is 90°, and thus a smaller angle means there is more tilt. Therefore, it is also called low angle deposition. In all cases, the particles were deposited at the top surface and the side wall of the chamber together, and the deposition form was a cone shape following a specific slope and path. The slope follows the tangent equation,  $y = 2 \tan \theta x + \alpha$ . The heights, which are the dimensions from the bottom to the deposition starting point of the side wall (H value in the inset of Figure 2d), were compared according to the tilt angles and aspect ratios. For the same aspect ratio, a lower tilted angle yields less deposition of the evaporation material inside the chamber wall (Figure 2a,b). When the same tilted angle is selected, a higher aspect ratio can give a larger process margin. If the aspect ratio is less than 1, for example, a 0.5 aspect ratio, a very low angle below  $45^{\circ}$  is required without any deposition on the bottom device structure (Figure 2c). In the same simulation cycles at an aspect ratio of 1, the horizontally deposited thicknesses from the side walls (S value in the inset of Figure 2d) were approximately 150, 120, and 105 nm at 30°, 40°, and 45°, respectively. This shows that the smaller angles resulted in large covering of the hole by thicker lateral deposition. Therefore, a smaller angle can be recommended for vacuum sealing. The calculated height from the simulation is depicted in the graph (Figure 2d,e). The maximum height is nearly 200 nm at an aspect ratio of 1.5 and a tilt angle of 30°. Because a higher aspect ratio can induce a larger chamber volume, although it can provide a better process margin, the proper aspect ratio and angle should be considered to fabricate the vacuum chamber. Based on the simulation results, the vacuum chamber was fabricated and compared experimentally.

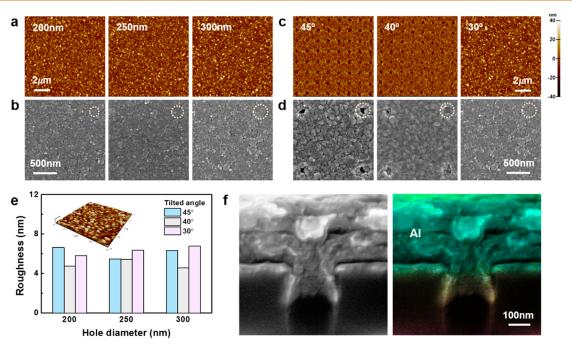

Cylinders with aspect ratios of 1, 1.2, and 1.5—where the hole diameters were designed to be 300, 250, and 200 nm, respectively—were fabricated and the height was fixed at 300 nm. The tilted angles were selected as 30°, 40°, and 45° (Figure 3a). An array structure was fabricated to evaluate the

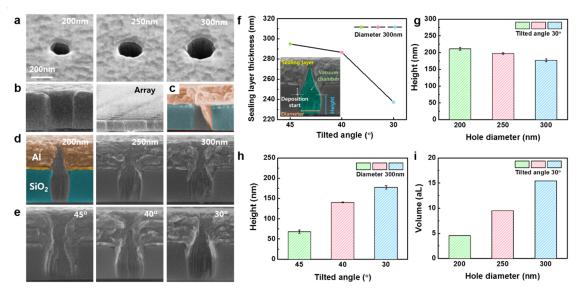

Figure 4. Results of the top sealing layer of the vacuum chamber: (a) atomic force microscope (AFM) image and (b) SEM image of tilted angle 30° according to the hole diameter. (c) AFM and (d) SEM images of hole diameter of 300 nm according to the tilted angle. In (b) and (d), the yellow broken line means the initial hole diameters before tilted angle evaporation. (e) Roughness characteristics by the hole diameter. (f) SEM and EDS results of the interior of vacuum chamber structure.

uniformity (Figure 3b). The cylinder array showed good uniformity in the process. During SiO<sub>2</sub> dry etching for cylinder fabrication, the bottom SiO2 oxide such as substrate oxide or gate oxide of the transistor may be etched or damaged. It can be solved through sophisticated process control by using such an end point detector which makes it possible to control the etch end point carefully, and it can have ~1 nm margin. In addition, the problem can be solved by using different oxides for the under layer such as Al<sub>2</sub>O<sub>3</sub> and HfO<sub>2</sub> or fabricating the cylinder using polymers such as polyimide (PI) and SU-8. Rotation of the substrate during the evaporation process is recommended for uniform vacuum sealing. Otherwise, the material will be deposited on one side of the wall, which impedes the sealing of the cylinder structure (Figure 3c). The deposition conditions such as the deposition thickness, amount of evaporation source, rotation speed, and deposition rate were the same for all conditions. The chamber shapes resemble a water drop in all cases, which was predicted by the simulation. For the tilted angle of 30°, the cylinders were sealed well at all aspect ratios (Figure 3d). However, as predicted from the results of Figure 2, with a smaller angle and thus faster vacuum sealing, it was confirmed that the cylinders were not completely blocked at  $40^{\circ}$  and  $45^{\circ}$  and were only sealed at 30°, when the aspect ratio was 1 (Figure 3e). Since the sealing layer was deposited with different angles, the thickness of the final sealing layers was different. There is a thickness difference in the top sealing layer between the target thickness controlled using a quartz crystal monitor and the actual thickness on the sample (Figure 3f). The top sealing layer thickness was increased as the tilt angle was decreased. When the target thickness of the sealing layer was set as 400 nm monitored by the thickness monitor, but at all angles, the thicknesses were less than this, and the largest difference was about 38% less than the target thickness. Therefore, to achieve perfect sealing of the vacuum and to obtain a uniform top sealing layer, it is

necessary to adjust the actual deposition considering the tilt angle for evaporation. In order to check the chamber volume, the actual height was extracted from a scanning electron microscope (SEM) analysis (Figure 3g,h). From the definition of the trigonometric functions, the height can be expressed by the following equation: height = cylinder thickness diameter/tan (90 -  $\theta$ ). Deposition starts at the high starting point with an increasing aspect ratio and a decreasing tilted angle. The deposition slope becomes more gradual by the slope of 2 tan  $\theta$  as the tilted angle is decreased, as mentioned previously. The highest height is over 200 nm under the conditions of an aspect ratio of 1.5 and an angle of 30°, and the height also is close to 200 nm at aspect ratios of 1.2 and 1 at 30°. The errors at other points for each condition are very small (i.e., less than 5 nm). The volumes of the vacuum chamber have several 10<sup>-18</sup>L levels, the attoliter [aL] scale (Figure 3i). As a result, we can fabricate an ultrasmall size vacuum chamber with a ~nm2 level of area with ~aL level of

The sealing layer was deposited in a high vacuum state  $(\sim 10^{-6} \text{ Torr})$ . If collapse does not occur and there are no nondeposited areas of the top sealing layer, the inside of the nano chamber pressure will be almost the same with the evaporation process pressure. The surface topology was assessed to confirm whether the vacuum sealing film was well sealed at each condition without any nondeposited areas and endured without breaking due to the different pressures with air. The results for all conditions are presented in a table in Figure S1. The top sealing layer was perfectly covered at 30° for all hole diameter conditions (Figure 4a,b). For other cases of 40° and 45° with an aspect ratio of 1, the holes were not covered well (Figure 4c,d). In the 40° case, the holes were more covered than those at 45°, but the hole structure still exists. However, this does not necessarily mean that the structure is not sealed in a vacuum state because the lower

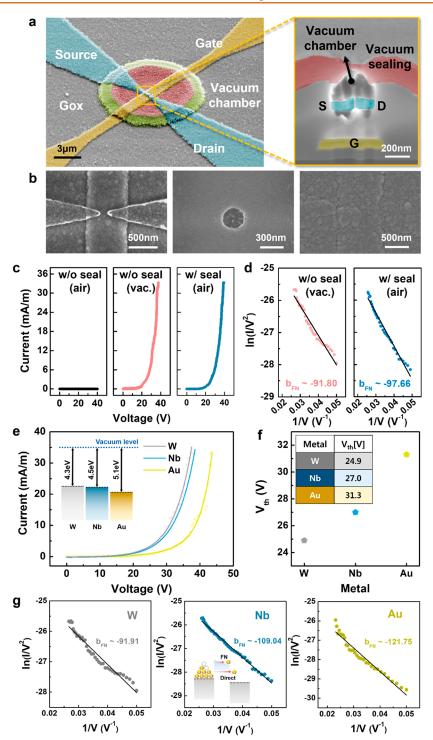

Figure 5. SEM images of vacuum tunneling transistor with vacuum chamber. (a) Appearance of the entire transistor and magnified images inside the vacuum chamber. (Right) Cross-section SEM image of nano vacuum tube after FIB. S, D, and G mean source, drain, and gate, respectively. (b) Step-by-step fabrication results: Tunneling transistor (left), after the formation of nano cylinder (center), and after sealing (right). (c) Electrical characteristics of vacuum tunneling diode (left and middle) without (w/o) vacuum chamber measured under atmospheric pressure and a high vacuum, respectively (right), with (w/) vacuum chamber measured in atmospheric pressure. (d) Properties of FN tunneling mechanism under (left) same conditions with middle of (c) and (right) same conditions with right of (c). (e) Electrical performance of the vacuum tunneling diode according to the use of different metals (inset) and work functions of the metals. (f)  $V_{th}$  and (g) FN tunneling characteristics of each metal.

region of the hole can be covered first due to the slope equation, even if the upper region is not covered perfectly. Therefore, when the thickness of the top sealing layer is increased, the whole area can be well-covered and uniform. After the sealing process by tilted evaporation, the sealing film

is quite uniform. The roughness is less than 8 nm (Figure 4e). This top sealing layer can be used for any material that can be tilted angle evaporation, even the insulator layer. However, it can cause critical issues for device operation such as electrical short or cutoff if it is deposited at the bottom of the vacuum

chamber where the main device is located. In the present case, a conductive aluminum (Al) was chosen as a sealing material. Therefore, it is important to deposit the sealing layer only at the side of the vacuum chamber to prevent an electrical short. So, the vacuum chamber was analyzed using an energy-dispersive spectrometer (EDS) to assess whether the sealing material was deposited at the chamber bottom (Figure 4f). Al appeared only at the top of the cylinder. As a result, there is no critical issue in combining the vacuum chamber with vacuum devices. Additionally, it is important to optimize the chamber structure, such as tilted angle and aspect ratio. To measure the electrical characteristics of vacuum tunneling devices with the reliable sealing process, we chose a nano chambered structure with an aspect ratio of 1 and a tilted angle of 30° for ideal vacuum sealing.

Nano Vacuum Tube. The electrical characteristics of nano vacuum tunneling devices were studied. Here, the current units were expressed as mA/m to current normalization at the electrode edge of the sharp tip structure. Recently, the dimensional part of the transistor has become one of the important factors to compare the transistor with conventional transistors. It defined current normalization in conventional transistors such as metal-oxide-semiconductor field effect transistors (MOSFET) and thin film transistors (TFT). 32,57-60 Because the current flows follow the electric field (or potential) in the channel. It is affected by the length or distance of the source, drain, and gate electrode. Even in vacuum devices, it depends on the electrode's sharpness. Therefore, according to the electrode sharpness, the localized electric field is changed.<sup>61-63</sup> However, there is no big difference in the single electrode apex. So, the units were used to normalize the current flow according to the width and curvature of the sharp tip electrode. In addition, it is easy to increase the overall understanding of vacuum transistors. First, the SEM images of a nano vacuum transistor with the sealing structure are presented (Figure 5a). The inside of the nano vacuum tube was confirmed after focused ion beam (FIB) etching (Figure 5a, right). It maintains well the vacuum chamber structure studied in the previous section, and it shows the existence of a vacuum tunneling transistor inside of the vacuum chamber. The SEM images of each fabrication step of nano vacuum tubes are shown in Figure 5b. The cylinder nano hole was well aligned to the vacuum device structure. After the sealing process by tilted evaporation, the cylinder structure was well sealed by the Al sealing material without collapse. First, the diode function was studied. The anode and cathode were fabricated as a sharp tip structure to maximize the electrical field by a structural effect. 22,23,54,64,65 The sharp tip structure can enhance the electrical field approximately by more than 2fold at the point of the tip relative to a flat electrode structure. 11,33 Before vacuum sealing, the tunneling diode was measured in air and vacuum state using a vacuum test chamber (Figure 5c, left and middle, respectively). Without the sealing process, there was quite a low current flow below 50 V, even though the anode and cathode gap was approximately 100 nm, which was slightly larger than the MFP. However, it can be operated at atmospheric pressure when applied high anode voltage up to 180 V (Figure S2). In recent trends, the low turnon voltage is essential for low power consumption. However, the diode's turn-on voltage is too high. It causes the metal meting which has a low melting point, and the electrodes can be damaged or broken down permanently. Therefore, it is difficult to realize the tunneling device without a vacuum

system, although in theory, a quite small gap between electrodes can induce the tunneling effect under air conditions. In the vacuum test chamber, the diode was operated well. After the nano sealing process, the sealing vacuum diode was measured in air as well (Figure 5c, right). It showed similar operation results even without the vacuum pumping system as well as in atmosphere conditions. Additionally, the operating mechanism of the nano vacuum sealing diodes follows the FN tunneling mechanism well (Figure 5d). The nano vacuum sealing structure effectively maintained the high vacuum state. Below 2-3 V/m of the electric field, FN tunneling does not occur. Therefore, the operating mechanism was studied over the 20 V region. We can extract the slope values of the FN plot  $(b_{\rm FN})$ , and from this value, the field enhancement factor  $(\beta)$ can be extracted.<sup>28</sup> The  $\beta$  is defined as the ratio of the maximum electric field at the electron emitter and the applied electric field. The factor is related to the electrode's geometric parameters such as radius and length. It is calculated from eq

$$b_{\rm FN} = \frac{0.95B\varnothing^{3/2}}{\beta} \tag{2}$$

Here,  $B = 6.87 \times 10^7$  and  $\emptyset$  is the work function of metal. The  $\beta$  is affected in electron tunneling, and a higher value means more electron emission. It is increased as a decrease the electrode gap and increase the electrode curvature because it is related to tip radius (r) and electrode gap (d),  $\beta \approx \frac{1}{r}$ , and  $\beta \approx \frac{1}{4}$ , respectively. The vacuum tunneling diode was studied according to the electrode gap, and  $\beta$  was calculated and plotted.55 The electron emission can be increased by decreasing the tunneling distance by reducing the electrode gap (Figure S3).67 From this equation, electron emission is also affected by the work function of materials and the device structure such as the electrode gap or sharpness.<sup>68</sup> Various metal materials, specifically, tungsten (W), niobium (Nb), and gold (Au), were studied for vacuum tunneling with a diode structure. As tungsten has a small work function, more electron tunneling occurs at the same voltage, and a small threshold voltage  $(V_{th})$  is induced (Figure 5e,f).<sup>69</sup> Tunneling diodes using the three different metals were also operated following the FN tunneling mechanism (Figure 5g). In addition, the  $b_{FN}$ values can be compared with  $V_{\rm th}$  by following eq 3.66

$$V_{\rm th} pprox \left[ rac{b_{

m FN}}{\ln\left(rac{k_{

m FN}}{I_{

m on}}

ight)}

ight] pprox \left[ rac{0.95B\varnothing^{3/2}}{eta \ln\left(rac{k_{

m FN}}{I_{

m on}}

ight)}

ight]$$

(3)

Here,  $k_{\rm FN}\approx 2.5\times 10^6$ ,  $I_{\rm on}$  is on current. From this equation, it can be seen that  $V_{\rm th}$  is directly proportional to  $b_{\rm FN}$ ,  $V_{\rm th}\approx b_{\rm FN}$ . Therefore, as  $b_{\rm FN}$  increases,  $V_{\rm th}$  also increases. Additionally, from the equation,  $b_{\rm FN}$  is inversely proportional to  $\beta$  and linearly proportion to  $\varnothing^{3/2}$ . Therefore, when the work function of the electrode material is lowered,  $V_{\rm th}$  is also lowered (Figure S4a). In a diode structure, the current can include the leakage current especially the surface leakage at low voltage region. Recently, the analysis of direct tunneling which appeared in the low voltage region has been studied. However, it is still difficult to separate surface leakage present in current characteristics. The device operation was confirmed more detail from the behavior change point at electrical characteristics as a semilog scale whether the point is FN

Figure 6. (a) Schematic images of vacuum tunneling mechanism and energy band bending. (b) Visualized electric field simulation of the nano vacuum tube to show the  $V_{\rm g}$  effect at fixed  $V_{\rm d}$  of 20 V and (right) the numerical electric field values according to the  $V_{\rm d}$  and  $V_{\rm g}$ . (c,d) Electrical characteristic of vacuum tunneling transistor measured in a test vacuum chamber before vacuum sealing. (Inset)  $V_{\rm th}$  result at each  $V_{\rm g}$ . (e) FN tunneling operating mechanism of the vacuum tunneling transistor. (f)  $I_{\rm gs}$  characteristic of the vacuum tunneling transistor. Geometrical effect of vacuum tunneling transistor: (g)  $I_{\rm ds}$  according to the different source and drain electrode gap and (h) field enhancement factor by the effect of the curvature of the tips at each electrode gap. (Inset) SEM images of the electrode tip at different curvatures, and the values are  $b_{\rm FN}$ .

tunneling or leakage like current flow (Figure S5). The voltage value in the change point is 19 V, and the FN tunneling appeared over  $0.054 \, {\rm V^{-1}}$  of 1/V which is nearly  $18.52 \, {\rm V}$ . These two points are almost the same. As a result, it can be also confirmed that the vacuum tunneling diode was operated following the FN mechanism over the 20 V region.

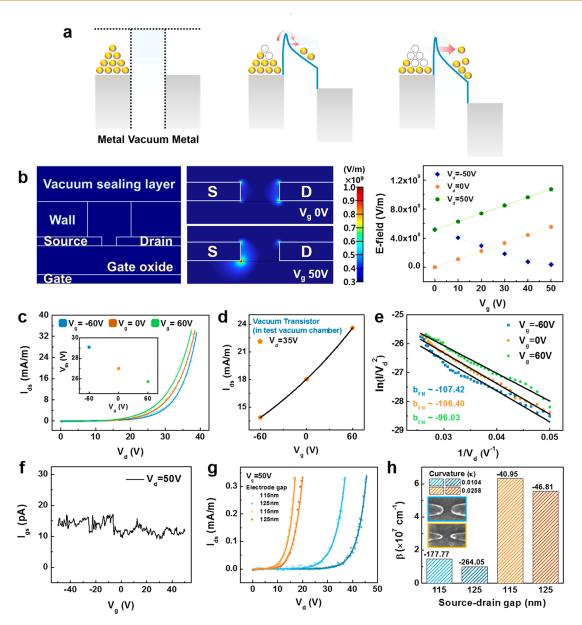

For the operation of the vacuum transistor, the potential barrier can be controlled and more energetic electrons at the source can be emitted to the vacuum and travel to the drain when the gate bias is applied (Figure 6a). The electrical field distribution was simulated with the multiphysics simulation program (Figure 6b). The localized electric field at the source edge was enhanced by increasing the gate voltage  $(V_g)$ . The thickness of the tunneling energy barrier can be reduced due to

the increased channel potential. In addition, once the electrons are released, they are attracted to the drain by the drain voltage  $(V_{\rm d})$ . Field emission characteristics of the vacuum transistor without sealing were measured in a test vacuum chamber system (Figure 6c). With more positive  $V_{\rm g}$  applied,  $V_{\rm th}$  decreased during the  $V_{\rm d}$  sweep. At the same  $V_{\rm d}$ , more current flows by increasing the  $V_{\rm g}$  (Figure 6d). The operation of this vacuum transistor also follows the FN mechanism (Figure 6e). In addition, they have small gate leakage current  $(I_{\rm gs})$  of nano vacuum tunneling transistors measured in a test vacuum chamber. The  $I_{\rm gs}$  levels were approximately  $10^{-14}-10^{-11}$  A (Figures 6f and S6a). The  $I_{\rm gs}$  level can be neglected, and it does not greatly affect device operation since it is too small compared with the drain current  $(I_{\rm ds})$ . The  $I_{\rm gs}$  is dependent on

Figure 7. Electrical characteristics of nano vacuum tube according to the (a)  $V_{\rm d}$  and (b)  $V_{\rm g}$ . (c,d)  $I_{\rm ds}$  results according to exposure to various light sources. (e) FN tunneling operating mechanism under each light source. (f) Temperature dependency. (g) Reliability results of vacuum chamber with high vacuum sealing. (h) Stability results of the nano vacuum tube. (Inset)  $I_{\rm ds}$  by  $V_{\rm d}$  result.

the position of the gate relative to the source and drain terminal which means it was affected by the overlap dimension of the source, drain, and gate.  $^{20,56}$  The increased  $I_{\rm gs}$  causes device performance degradation and increases power consumption. To reduce the  $I_{\rm gs}$  the vacuum tunneling transistor was fabricated with a small overlap dimension and the gate electrode was positioned in the center of the source and drain electrode with a symmetrical structure. The overlap dimension of the source and gate is very small, approximately  $3\times 10^{-14}$  m². The alignment mismatch was minimized to increase the dimensional accuracy. Therefore, the devices can have small  $I_{\rm gs}$ . Moreover, the electrical properties can be improved by optimization of the device structure, such as the electrode

gap and tip sharpness. When the source and drain electrode gap are decreased the  $V_{\rm th}$  voltage is also decreased (Figure 6g). Therefore, the device can be turned on at a low voltage. Two types of tunneling devices with different tip sharpnesses were fabricated. The curvature ( $\kappa$ ) is the reciprocal of the radius, and then a large  $\kappa$  value means a sharper tip structure. The  $\beta$  value was enhanced approximately 4-fold when  $\kappa$  is  $\sim$ 0.02 at the same gap condition (Figure 6h). Larger curvature of the electrode results in a large  $\beta$ . Therefore, if the electrode becomes sharper, the electrical properties can be enhanced, consistent with the results observed for the tunneling diode. All results of vacuum transistors also follow the tendency of the relation to  $V_{\rm th}$  and  $b_{\rm FN}$ . Therefore,  $\beta$  increases

through increasing tip sharpness and decreasing electrode gap,  $b_{\rm FN}$  decreases, and the  $V_{\rm th}$  decreases (Figure S4b-d). In addition, the operation of the vacuum tunneling transistor can be affected by the vacuum channel pressure. The transistor was measured in various pressures of a test vacuum chamber from air to high vacuum ( $10^{-6}$  Torr) (Figure S7). At each  $V_{\rm g}$  and  $V_{\rm d}$ condition,  $I_{ds}$  was increased as the pressure decreased, and the  $V_{\rm th}$  was decreased as an increase vacuum quality of the test vacuum chamber. Because as the vacuum level increases, the probability of scattering and collision of emitted electrons was decreased due to the small number of gas molecules. Although a vacuum region was used as the electron transport medium, the device is not completely free of scattering or trapping. To support and confirm more about the effect of the trap site, the hysteresis of the device operation was measured when the voltage was applied from 0 to 40 V and returned to 0 V (Figure S8). Hysteresis is the dependence of the state of a system on its history. If there are any trap sites in the vacuum channel, the electron is trapped, and large hysteresis may appear. There is almost no hysteresis. Therefore, it is confirmed that there is almost no electron trapping in our vacuum transistor.

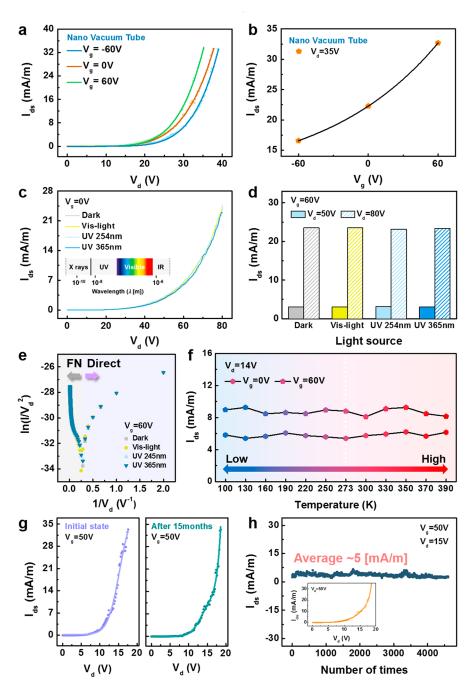

Stability and Reliability Test under Various External Environments. After the nano sealing process, the electrical characteristics of the transistor were measured in atmospheric conditions. As mentioned previously, the nano vacuum chamber was fabricated by a tilted evaporation process. Since the nano vacuum chamber effectively sustained the high vacuum state of the transistor structure, all characteristics were almost similar to those of the previous transistor tested in the test vacuum chamber system (Figure 7a,b). But the current flow of the nano vacuum tube was slightly increased because the top metal sealing layer was operated as a floating electrode. From the electric field simulation result, the localized electrical field at the top of the source edge of the source electrode was increased nearly 4-fold (Figure S9). As a result, the probability of electron emission was increased, and the current flow was slightly increased. In addition, the nano vacuum tube has a small  $I_{gs}$  value approximately  $10^{-14}$  A level (Figure S6b). The nano vacuum tunneling tube has a structure that can protect the vacuum channel from the outside, and it can withstand various external environments. Therefore, device characteristics were studied in various extreme environments such as high-energy light-exposure conditions and wide working temperatures. Due to photovoltaic and photoelectric effects, semiconductor devices suffer from abnormal behavior when light is exposed. Even the semiconductor device can be damaged by high energy light. Therefore, additional passivation or packaging is essential. For the vacuum tunneling structure, it can be robust to the photovoltaic effect since the main materials of the device are metals with a vacuum barrier. However, a photoelectric effect by high energy light was a problem in old vacuum tubes based on glass sealing. Fortunately, because of the Al sealing layer, our system can maintain the reliable performance of the tunneling transistor under harsh light exposure conditions. Various light sources, specifically visible light (white source) and UV of 254 and 365 nm wavelength, were exposed during transistor operation, and the change of electrical performance including that in a dark (without light) state was compared. The electrical performance of the tunneling device is almost identical under different drain bias conditions (Figure 7c,d). To confirm their operating mechanism, the result was confirmed by FN plot analysis (Figure 7e). There is no big change in the operation of the

transistor for various light sources. However, in the range of less than  $0.2~{\rm V}^{-1}$  of  $1/V_{\rm d}$ , they have a slight difference. The results were strictly fitted and distinct by separating the  $V_{\rm d}$  range. They have two operating mechanisms of Schottky (Thermionic) emission (SE) and FN tunneling emission (Figure S10). The Schottky emission is dominant from 5 to 13 V of  $V_{\rm d}$ , and over this voltage range, the FN tunneling emission is dominant because some electrons can be emitted into the vacuum by overcoming the potential barrier not penetrating due to the applied high voltage. Additionally, the penetration depth of electron and proton versus X-ray energy can be calculated from the energy loss as in eq 4.70

penetration depth =

$$\frac{E_0^{5/3}}{\lambda_g \times 5 \times 2^{5/3} \pi a^{1/3} e^{10/3} NZ}$$

(4)

Here,  $\lambda_g$  is constant at 0.182, a is the effective screened radius of the atom, and  $N = N_a \rho / A$ ;  $N_a$  is the Avogadro number of  $6.023 \times 10^{23}$ , and A is atomic weight. Additionally,  $E_0$  is the beam energy, and Z is the atomic number. The penetration depth of electrons, protons, photons, and other ions depends on their energy. The depth is determined by their stopping power which is related to atomic mass and target solid materials. The stopping power is decreased with increasing the atomic number. Therefore, we can estimate the mean penetration depth versus the radiation energy in the top Al sealing layer (Figure S11). As a result, it is estimated that the structure blocks approximately 5 keV of X-ray.<sup>71</sup> Recently, a wide working temperature is also important because of various applications of electrical devices such as electric vehicles or high speed calculation with big data. Si-based transistors have shown some limits under severe temperature conditions. The vacuum tunneling transistor was measured under a wide working temperature. The change in characteristics was confirmed by measuring from 100 K (-173 °C) up to 390 K, which is higher than the value of 353 K (80 °C) which is generally referred to as a high temperature in device operation. All results confirmed that the sealing of the vacuum transistor did not have any significant issue in the wide temperature range of 100 to 390 K (Figure 7f). Nonetheless, given that 100 K is the lowest stable state in our liquid nitrogen cooling system and it is the limit of measurement in this experiment, we expect that the device can work well at much lower temperature conditions considering the structure and working principle. Finally, the reliability of the vacuum chamber and the stability of the tunneling transistor were confirmed. Reliability is determined by how long the vacuum chamber can be maintained for device operation. The stability is evaluated by determining how many times the tunneling transistor could be turned on and off repeatedly. The transistor was measured again 15 months later and the test was still continuing (Figure 7g). The electrical characteristics were almost the same. To measure the stability, an acceleration test was conducted with the transistor (Figure 7h). The  $V_g$  and  $V_d$  were fixed at 50 and 15 V, respectively, and the current level was around 5 mA/m. Turn on and off was repeated at 1 s intervals, and the current level was well sustained. As a result, it is expected that the nano tunneling vacuum tube can be operated stably.

# CONCLUSION

We proposed a nano vacuum tunneling tube employing a nano vacuum chamber using tilted angle evaporation to operate vacuum devices in atmospheric pressure. Using Python, the ACS Nano www.acsnano.org Article

movement path and deposition form of particles during tilted angle evaporation for vacuum sealing were visualized. The nano vacuum tube was fabricated by general silicon processing similar to MOSFET. It is highly compatible with existing CMOS fabrication processes, and there are few process restrictions. Therefore, it can be embedded easily in other integrated circuit components based on Si. Additionally, the fabrication process of the nano vacuum chamber is very simple, and it has high uniformity in an array structure. The vacuum chamber has an ultrasmall chamber volume of several tens of 10<sup>-18</sup> L, and a high vacuum can be maintained without the collapse of the vacuum sealing layer. Therefore, it is suitable for the trend of device miniaturization. The vacuum tunneling diode and transistor combined with the nano vacuum chamber were operated according to the FN tunneling mechanism in atmospheric pressure without a vacuum measurement system. Furthermore, it has high reliability and stability, despite the fact that the fabrication process of vacuum sealing is very simple and easy. It is possible to maintain a stable vacuum, and the devices could be operated for a very long time of more than 15 months. The transistor could withstand an extreme external environment with UV exposure and a wide temperature range. Therefore, it can be used as a next-generation device operating in harsh environments, such as those encountered in aerospace applications.

#### **METHODS**

Fabrication of Nano Gap Vacuum Tunneling Transistor. The vacuum tunneling transistor was fabricated on a silicon substrate with thermally grown SiO<sub>2</sub>. The gate electrode was patterned by electron beam lithography (EBL). For the electron beam resist (ER) a 950 K PMMA A4 was used. A charge dissipating agent was co-coated to minimize the electron beam charging effect for the nano gap. Gate materials of Cr and Au were deposited using a thermal evaporation system and lift off. SiO<sub>2</sub> was used as a gate oxide, and it was deposited using plasma enhanced chemical vapor deposition (PECVD). Source and drain electrodes were also patterned using EBL to obtain a gap that was several tens of nanometers in size. For the electrode material, W was deposited by a magnetron sputtering system and lift off. All contact pads of the electrode were fabricated by photo lithography and deposited using the same materials and methods.

Fabrication of Nano Vacuum Chamber. The nano vacuum chamber was fabricated on the vacuum transistor. The nano chamber was designed with a cylindrical structure. The wall of the vacuum chamber was SiO<sub>2</sub> deposited by PECVD. The nano scale hole was patterned for the vacuum cylinder using EBL. Also, the ER was 950 K PMMA A4. Al was etched using a cluster etching system, and SiO<sub>2</sub> was dry etched using a reactive ion etcher (RIE). SiO<sub>2</sub> etching was controlled elaborately by using the end point detector. The vacuum chamber was sealed by tilted angle evaporation using a thermal evaporation system. Al was used as a vacuum sealing material with 400 nm thickness. During evaporation, the holder was rotated to obtain a uniform thin film.

Simulation and Measurement of Electrical Characteristics. The particle path and deposition form during tilted evaporation were simulated by using Pygame, which is written in Python. The electric field simulation was performed by using COMSOL multiphysics. The electrical characteristics of the vacuum devices were measured by using an I-V measurement system (Keithley 4200-SCS) with a vacuum chamber probe station.

# **ASSOCIATED CONTENT**

### **Data Availability Statement**

All data are available in the main manuscript or Supporting Information.

## **5** Supporting Information

The Supporting Information is available free of charge at https://pubs.acs.org/doi/10.1021/acsnano.3c02916.

Surface topology of nano vacuum chamber after vacuum sealing, vacuum diode operation in atmospheric pressure, geometrical effect of vacuum tunneling diode, comparison of threshold voltage and slope of FN plots, operating behavior of vacuum tunneling diode, leakage current of vacuum tunneling transistor, electrical properties of vacuum tunneling transistor according to the pressure, hysteresis of vacuum tunneling transistor, e field simulation according to the vacuum sealing, operating mechanism of vacuum transistor under light exposure, penetration depth in aluminum target, and comparison of various vacuum tunneling devices (PDF)

#### **AUTHOR INFORMATION**

#### **Corresponding Author**

Jae Eun Jang — Department of Electrical Engineering and Computer Science (EECS), Daegu Gyeongbuk Institute of Science and Technology (DGIST), Daegu 42988, Republic of Korea; orcid.org/0000-0002-8523-1785; Phone: +82 53 785-6312; Email: jang1@dgist.ac.kr

#### **Authors**

Su Jin Heo – Department of Electrical Engineering and Computer Science (EECS), Daegu Gyeongbuk Institute of Science and Technology (DGIST), Daegu 42988, Republic of Korea

Jeong Hee Shin – Electronic Convergence Materials Center, Korea Institute of Ceramic Engineering and Technology (KICET), Jinju 52851, Republic of Korea

Byoung Ok Jun – Samsung Electronics Foundry Business Department, Hwaseong 18448, Republic of Korea

Complete contact information is available at: https://pubs.acs.org/10.1021/acsnano.3c02916

#### Notes

The authors declare no competing financial interest.

## **ACKNOWLEDGMENTS**

This research was supported by the Basic Science Research Program through the National Research Foundation of Korea (NRF) funded by the MSIT (No. 2020R1A2C1006295, No. 2021R1A4A1028652) and Samsung Electronics.

# **ABBREVIATIONS**

CMOS, complementary metal oxide semiconductor; MOS-FET, metal oxide semiconductor field effect transistors; MFP, mean free path; UV, ultraviolet; FN, Fowler–Nordheim; SE, Schottky emission; S, source; D, drain; G, gate;  $V_{\rm th}$ , threshold voltage;  $V_{\rm d}$ , drain voltage;  $V_{\rm g}$  gate voltage;  $I_{\rm ds}$ , source-drain current;  $I_{\rm gs}$ , (source-gate) leakage current;  $I_{\rm on}$ , on current;  $b_{\rm FN}$ , slope of FN plot

#### **REFERENCES**

(1) Shin, J. H.; Heo, S. J.; Yang, J. H.; Kim, H. S.; Jung, J. E.; Kwon, H.-J.; Jang, J. E. Switching Behavior in a Vertical Tunneling Transistor by Tunneling Mechanism Transition and Floating Electrode Structure. ACS Applied Electronic Materials 2020, 2, 2461–2469.

- (2) Dodd, P. E.; Shaneyfelt, M. R.; Schwank, J. R.; Felix, J. A. Current and Future Challenges in Radiation Effects on CMOS Electronics. *IEEE Trans. Nucl. Sci.* **2010**, *57*, 1747–1763.

- (3) Han, J.-W.; Seol, M.-L.; Moon, D.-I.; Hunter, G.; Meyyappan, M. Nanoscale Vacuum Channel Transistors Fabricated on Silicon Carbide Wafers. *Nature Electronics* **2019**, *2*, 405–411.

- (4) Han, J.-W.; Oh, J. S.; Meyyappan, M. Cofabrication of Vacuum Field Emission Transistor (VFET) and MOSFET. *IEEE Transactions on Nanotechnology* **2014**, *13*, 464–468.

- (5) Han, J. W.; Moon, D. I.; Meyyappan, M. Nanoscale Vacuum Channel Transistor. *Nano Lett.* **2017**, *17*, 2146–2151.

- (6) Khoshkbijari, F. K.; Sharifi, M. J. Finger Gate Vacuum Channel Field Emission Transistors: Performance and Sensitivity Analysis. *IEEE Trans. Electron Devices* **2021**, *68*, 5250–5256.

- (7) Bareiß, M.; Ante, F.; Kälblein, D.; Jegert, G.; Jirauschek, C.; Scarpa, G.; Fabel, B.; Nelson, E. M.; Timp, G.; Zschieschang, U.; Klauk, H.; Porod, W.; Lugli, P. High-Yield Transfer Printing of Metal-Insulator-Metal Nanodiodes. *ACS Nano* **2012**, *6*, 2853–2859.

- (8) Shih, P.-C.; Rughoobur, G.; Engel, Z.; Ahmad, H.; Doolittle, W. A.; Akinwande, A. I.; Palacios, T. Stable and High Performance AlGaN Self-Aligned-Gate Field Emitter Arrays. *IEEE Electron Device Lett.* **2022**, 43, 1351–1354.

- (9) Shi, H.; Ding, L.; Zhong, D.; Han, J.; Liu, L.; Xu, L.; Sun, P.; Wang, H.; Zhou, J.; Fang, L.; Zhang, Z.; Peng, L.-M. Radiofrequency Transistors Based on Aligned Carbon Nanotube Arrays. *Nature Electronics* **2021**, *4*, 405–415.

- (10) Yang, S. J.; Park, K. T.; Im, J.; Hong, S.; Lee, Y.; Min, B. W.; Kim, K.; Im, S. Ultrafast 27 GHz Cutoff Frequency in Vertical WSe<sub>2</sub> Schottky Diodes with Extremely Low Contact Resistance. *Nat. Commun.* **2020**, *11*, 1574.

- (11) Yang, J. H.; Shin, J. H.; Kim, S.; Pyo, G.; Jang, A. R.; Yang, H. W.; Kang, D. J.; Jang, J. E. Geometrically Enhanced Graphene Tunneling Diode With Lateral Nano-Scale Gap. *IEEE Electron Device Lett.* **2019**, 40, 1840–1843.

- (12) Zhou, S.; Chen, K.; Cole, M. T.; Li, Z.; Li, M.; Chen, J.; Lienau, C.; Li, C.; Dai, Q. Ultrafast Electron Tunneling Devices-From Electric-Field Driven to Optical-Field Driven. *Adv. Mater.* **2021**, 33, No. e2101449.

- (13) Banerjee, S.; Zhang, P. Review of Recent Studies on Nanoscale Electrical Junctions and Contacts: Quantum Tunneling, Current Crowding, and Interface Engineering. *Journal of Vacuum Science & Technology A* **2022**, 40, No. 030802.

- (14) Cowell, E. W., 3rd; Alimardani, N.; Knutson, C. C.; Conley, J. F., Jr.; Keszler, D. A.; Gibbons, B. J.; Wager, J. F. Advancing MIM Electronics: Amorphous Metal Electrodes. *Adv. Mater.* **2011**, 23, 74–78

- (15) Suzuki, M.; Sagawa, M.; Kusunoki, T.; Nishimura, E.; Ikeda, M.; Tsuji, K. Enhancing Electron-Emission Efficiency of MIM Tunneling Cathodes by Reducing Insulator Trap Density. *IEEE Trans. Electron Devices* **2012**, *59*, 2256–2262.

- (16) Alimardani, N.; Conley, J. F. Step Tunneling Enhanced Asymmetry in Asymmetric Rectrode Metal-Insulator-Insulator-Metal Tunnel Diodes. *Appl. Phys. Lett.* **2013**, *102*, No. 143501.

- (17) Periasamy, P.; Guthrey, H. L.; Abdulagatov, A. I.; Ndione, P. F.; Berry, J. J.; Ginley, D. S.; George, S. M.; Parilla, P. A.; O'Hayre, R. P. Metal-Insulator-Metal Diodes: Role of the Insulator Layer on the Rectification Performance. *Adv. Mater.* **2013**, *25*, 1301–1308.

- (18) Lee, J. H.; Shin, D. H.; Yang, H.; Jeong, N. B.; Park, D. H.; Watanabe, K.; Taniguchi, T.; Kim, E.; Lee, S. W.; Jhang, S. H.; Park, B. H.; Kuk, Y.; Chung, H. J. Semiconductor-Less Vertical Transistor with  $I_{\rm ON}/I_{\rm OFF}$  of  $10^6$ . *Nat. Commun.* **2021**, *12*, 1000.

- (19) Wang, X.; Zheng, C.; Xue, T.; Shen, Z.; Long, M.; Wu, S. Nanoscale Vacuum Field Emission Triode with a Double Gate Structure. *IEEE Electron Device Lett.* **2022**, 43, 292–295.

- (20) Chen, T.; Hong, W.; Shen, C.; Fan, H.; Bai, N.; Sun, X. High Gain Double Gate Vacuum Emission Transistor with low Leakage Current. 2021 22nd International Vacuum Electronics Conference (IVEC) 2021, 1–2.

- (21) Feng, J.; Gong, Y.; Du, C.; Cross, A. High-Frequency Vacuum Electron Devices. *Electronics* **2022**, *11*, 817.

- (22) Sapkota, K. R.; Leonard, F.; Talin, A. A.; Gunning, B. P.; Kazanowska, B. A.; Jones, K. S.; Wang, G. T. Ultralow Voltage GaN Vacuum Nanodiodes in Air. *Nano Lett.* **2021**, 21, 1928–1934.

- (23) Nirantar, S.; Ahmed, T.; Ren, G.; Gutruf, P.; Xu, C.; Bhaskaran, M.; Walia, S.; Sriram, S. Metal-Air Transistors: Semiconductor-Free Field-Emission Air-Channel Nanoelectronics. *Nano Lett.* **2018**, *18*, 7478–7484.

- (24) Han, J.-W.; Seol, M. L.; Meyyappan, M. A Nanoscale Vacuum Field Emission Gated Diode with an Umbrella Cathode. *Nanoscale Adv.* **2021**, *3*, 1725–1729.

- (25) Han, J.-W.; Sub Oh, J.; Meyyappan, M. Vacuum nanoelectronics: Back to the Future?—Gate Insulated Nanoscale Vacuum Channel Transistor. *Appl. Phys. Lett.* **2012**, *100*, No. 213505.

- (26) Nirantar, S.; Patil, B.; Tripathi, D. C.; Sethu, N.; Narayanan, R. V.; Tian, J.; Bhaskaran, M.; Walia, S.; Sriram, S. Metal-Air Field Emission Devices Nano Electrode Geometries Comparison of Performance and Stability. *Small* **2022**, *18*, No. e2203234.

- (27) Forbes, R. G.; Deane, J. H. B. Reformulation of the Standard Theory of Fowler—Nordheim Tunneling and Cold Field Electron Emission. *Proceedings of the Royal Society A: Mathematical, Physical and Engineering Sciences* **2007**, 463, 2907–2927.

- (28) Guerrera, S. A.; Akinwande, A. I. Nanofabrication of Arrays of Silicon Field Emitters with Vertical Silicon Nanowire Current Limiters and Self-Aligned Gates. *Nanotechnology* **2016**, 27, No. 295302.

- (29) Ravariu, C. Vacuum Nano-Triode in Nothing-On-Insulator Configuration Working in Terahertz Domain. *IEEE Journal of the Electron Devices Society* **2018**, *6*, 1115–1123.

- (30) Pescini, L.; Tilke, A.; Blick, R. H.; Lorenz, H.; Kotthaus, J. P.; Eberhardt, W.; Kern, D. Nanoscale Lateral Field-Emission Triode Operating at Atmospheric Pressure. *Adv. Mater.* **2001**, *13*, 1780–1783.

- (31) Li, C.; Zhang, Y.; Cole, M. T.; Shivareddy, S. G.; Barnard, J. S.; Lei, W.; Wang, B. P.; Pribat, D.; Amaratunga, G. A. J.; Milne, W. I. Hot Electron Field Emission via Individually Transistor-Ballasted Carbon Nanotube Arrays. *ACS Nano* **2012**, *6*, 3236–3242.

- (32) Doyle, B. S.; Datta, S.; Doczy, M.; Hareland, S.; Jin, B.; Kavalieros, J.; Linton, T.; Murthy, A.; Rios, R.; Chau, R. High Performance Fully-Depleted Tri-Gate CMOS Transistors. *IEEE Electron Device Lett.* **2003**, *24*, 263–265.

- (33) Shin, J. H.; Yang, J. H.; Heo, S. J.; Jang, J. E. Geometric Effect in a Vertical Stack-up Metal-Insulator-Metal Tunnel Diode. *AIP Advances* **2017**, *7*, No. 105307.

- (34) Srisonphan, S. Nanogaps Mediated Field Effect-Controlled Field Emission Triode. ACS Applied Electronic Materials 2022, 4, 4857–4862.

- (35) Burns, D. W.; Guckel, H. Thin Films for Micromechanical Sensors. *Journal of Vacuum Science & Technology A: Vacuum, Surfaces, and Films* **1990**, *8*, 3606–3613.

- (36) Mastrangelo, C. H.; Yeh, J. H.-J.; Muller, R. S. Electrical and Optical Characteristics of Vacuum-Sealed Polysilicon Microlamps. *IEEE Trans. Electron Devices* **1992**, 39, 1363–1375.

- (37) Sune, C. T.; Jones, G. W.; Vellenga, D. Fabrication of Encapsulated Silicon-Vacuum Field-Emission Transistors and Diodes. *Journal of Vacuum Science & Technology B: Microelectronics and Nanometer Structures* **1992**, *10*, 2984–2988.

- (38) Burns, D. W.; Zook, J. D.; Horning, R. D.; Herb, W. R.; Guckel, H. Sealed-Cavity Resonant Microbeam Pressure Sensor. *Sensors and Actuators A* 1995, 48, 179–186.

- (39) Deka, N.; Subramanian, V. On-Chip Fully Integrated Field Emission Arrays for High-Voltage MEMS Applications. *IEEE Trans. Electron Devices* **2020**, *67*, 3753–3760.

- (40) Zook, J. D.; Herb, W. R.; Ahn, Y.; Guckel, H. Polysilicon Sealed Vacuum Cavities for Microelectromechanical Systems. *Journal of Vacuum Science & Technology A: Vacuum, Surfaces, and Films* **1999**, 17, 2286–2294.

- (41) Mastrangelo, C. H.; Muller, R. S. Vacuum-Sealed Silicon Micromachined Incandescent Light Source. *International Technical Digest on Electron Devices Meeting* **1989**, 503–506.

- (42) Karaulac, N.; Guerrera, S. A.; Akinwande, A. I.; Cole, M. T. Field Emission from Silicon Tips Embedded in a Dielectric Matrix. *International Vacuum Nanoelectronics Conference (IVNC)* **2017**, 142–143.

- (43) Rughoobur, G.; Jain, L.; Akinwande, A. I. Electron Transmission through Suspended Graphene Membranes Measured with a Low-Voltage Gated Si Field Emitter Array. *Nanotechnology* **2021**, 32, No. 285201.

- (44) Takahashi, K.; Ishida, H.; Sawada, K. Vacuum-Sealed Microcavity Formed from Suspended Graphene by Using a Low-Pressure Dry-Transfer Technique. *Appl. Phys. Lett.* **2018**, *112*, No. 041901.

- (45) Srisonphan, S.; Jung, Y. S.; Kim, H. K. Metal-Oxide-Semiconductor Field-Effect Transistor with a Vacuum Channel. *Nat. Nanotechnol.* **2012**, *7*, 504–508.

- (46) Wu, G.; Wei, X.; Zhang, Z.; Chen, Q.; Peng, L. A Graphene-Based Vacuum Transistor with a High ON/OFF Current Ratio. *Adv. Funct. Mater.* **2015**, 25, 5972–5978.

- (47) Li, C.; Cole, M. T.; Lei, W.; Qu, K.; Ying, K.; Zhang, Y.; Robertson, A. R.; Warner, J. H.; Ding, S.; Zhang, X.; Wang, B.; Milne, W. I. Highly Electron Transparent Graphene for Field Emission Triode Gates. *Adv. Funct. Mater.* **2014**, *24*, 1218–1227.

- (48) Zhan, F.; Yang, W.; Li, Z.; He, Y.; Yu, P.; Wang, B.; Wei, X. SiOx Tunneling Diode Arrays With Uniform Electron Emission. *IEEE Electron Device Lett.* **2022**, *43*, 1339–1342.

- (49) Jennings, S. G. The Mean Free-Path in Air. J. Aerosol Sci. 1988, 19, 159–166.

- (50) Spindt, C. A.; Holland, C. E.; Rosengreen, A.; Brodie, I. Field-Emitter Arrays for Vacuum Microelectronics. *IEEE Trans. Electron Devices* **1991**, 38, 2355–2363.

- (51) Spindt, C. A.; Brodie, I.; Humphrey, L.; Westerberg, E. R. Physical Properties of Thin-Film Field Emission Cathodes with Molybdenum Cones. *J. Appl. Phys.* **1976**, *47*, 5248–5263.

- (52) Brodie, I.; Spindt, C. A., Vacuum Microelectronics. In *Advances in Electronics and Electron Physics*; Academic Press, 1992; Vol. 83, pp 1–106.

- (53) Orvis, W. J.; Mcconaghy, C. F.; Ciarlo, D. R.; Yee, J. H.; Hee, E. W. Modeling and Fabricating Micro-Cavity Integrated Vacuum Tubes. *IEEE Trans. Electron Devices* **1989**, *36*, 2651–2658.

- (54) Velasquez-Garcia, L. F.; Guerrera, S. A.; Niu, Y.; Akinwande, A. I. Uniform High-Current Cathodes Using Massive Arrays of Si Field Emitters Individually Controlled by Vertical Si Ungated FETs—Part 2: Device Fabrication and Characterization. *IEEE Trans. Electron Devices* **2011**, *58*, 1783–1791.

- (55) Rughoobur, G.; Ilori, O. O.; Akinwande, A. I. Scanning Anode Field Emission Microscopy of a Single Si Emitter. *J. Vac. Sci. Technol. B* **2022**, *40*, No. 042803.

- (56) Tawfik, N. M. S.; Shaker, A.; Sayed, I.; Kamel, H.; Salem, M. S.; Dessouky, M.; Fedawy, M. Investigation of gate leakage current in TFET: A Semi-Numerical Approach. *Alexandria Engineering Journal* **2023**, 72, 169–180.

- (57) Fahad, H. M.; Smith, C. E.; Rojas, J. P.; Hussain, M. M. Silicon Nanotube Field Effect Transistor with Core-Shell Gate Stacks for Enhanced High-Performance Operation and Area Scaling Benefits. *Nano Lett.* **2011**, *11*, 4393–4399.

- (58) Zhang, Z.; Lin, Z.; Liao, P.-Y.; Askarpour, V.; Dou, H.; Shang, Z.; Charnas, A.; Si, M.; Alajlouni, S.; Shakouri, A.; Wang, H.; Lundstrom, M.; Maassen, J.; Ye, P. D. A Gate-All-Around in O Nanoribbon FET with Near 20 mA/m Drain Current. *IEEE Electron Device Lett.* **2022**, *43*, 1905–1908.

- (59) Hanna, A. N.; Hussain, M. M. Si/Ge Hetero-Structure Nanotube Tunnel Field Effect Transistor. *J. Appl. Phys.* **2015**, *117*, No. 014310.

- (60) Kim, S. H.; Kam, H.; Hu, C.; Liu, T.-J. K. Germanium Source Tunnel Field Effect Transistors with Record High  $I_{ON}/I_{OFF}$ . Symposium on VLSI Technology; IEEE, 2009.

- (61) Sim, H. S.; Lau, S. P.; Ang, L. K.; You, G. F.; Tanemura, M.; Yamaguchi, K.; Zamri, M.; Yusop, M. Field Emission from a Single Carbon Nanofiber at Sub 100 nm Gap. *Appl. Phys. Lett.* **2008**, 93, No. 023131.

- (62) Park, S.-S.; Park, D.-I.; Hahm, S.-H.; Lee, J.-H.; Choi, H.-C.; Lee, J.-H. Fabrication of a Lateral Field Emission Triode with a High Current Density and High Transconductance Using the Local Oxidation of the Polysilicon Layer. *IEEE Trans. Electron Devices* 1999, 46, 1283–1289.

- (63) Utsumi, T. Keynote Address: Vacuum Microelectronics: What's New and Exciting. *IEEE Trans. Electron Devices* **1991**, *38*, 2276–2283.

- (64) Han, J.-W.; Seol, M.-L.; Kim, J.; Meyyappan, M. Nanoscale Complementary Vacuum Field Emission Transistor. *ACS Applied Nano Materials* **2020**, *3*, 11481–11488.

- (65) Dall'Agnol, F. F.; Filippov, S. V.; Popov, E. O.; Kolosko, A. G.; de Assis, T. A. Determining the Field Enhancement Factors of Various Field Electron Emitters with High Numerical Accuracy. *J. Vac. Sci. Technol. B* **2021**, *39*, No. 032801.

- (66) Meng, D.; Guobin, S.; Akinwande, A. I. Silicon Field Emission Arrays with Atomically Sharp Tips: Turn-on Voltage and the Effect of Tip Radius Distribution. *IEEE Trans. Electron Devices* **2002**, 49, 2333–2342.

- (67) Monshipouri, M.; Walia, S.; Bhaskaran, M.; Sriram, S. Particle Tracking Simulation of an Air Channel Transistor. *AIP Advances* **2021**, *11*, No. 115209.

- (68) Xu, Z.; Bai, X. D.; Wang, E. G. Geometrical Enhancement of Field Emission of Individual Nanotubes Studied by in situ Transmission Electron Microscopy. *Appl. Phys. Lett.* **2006**, *88*, No. 133107.

- (69) Lee, Y.-H.; Choi, C.-H.; Jang, Y.-T.; Kim, E.-K.; Ju, B.-K. Tungsten Nanowires and Their Field Electron Emission Properties. *Appl. Phys. Lett.* **2002**, *81*, 745.

- (70) Kanaya, K.; Okayama, S. Penetration and Energy-Loss Theory of Electrons in Solid Targets. *J. Phys. D: Appl. Phys.* **1972**, *5*, 43.

- (71) Garrett, H. B.; Whittlesey, A. C. Guide to mitigating spacecraft charging effects; John Wiley & Sons, 2012; Vol. 3; pp 6–25.