Contents lists available at ScienceDirect

# Solid State Electronics

journal homepage: www.elsevier.com/locate/sse

# Source/drain metal-dependent oxygen scavenging from the viewpoint of the decoupling between source/drain resistance and threshold voltage in InGaZnO thin-film transistors\*

Seungki Kim<sup>a,1</sup>, Wonjung Kim<sup>a,1</sup>, Seong Hoon Jeon<sup>a</sup>, Changwook Kim<sup>a</sup>, Dong Myong Kim<sup>a,b</sup>, Sung-Jin Choi<sup>a</sup>, Yoon Jung Lee<sup>a</sup>, Dae Hwan Kim<sup>a,\*</sup>

#### ARTICLE INFO

# Keywords: Thin film transistor(TFT) Amorphous indium-gallium-zinc-oxide(a-IGZO) Amorphous oxide semiconductor(AOS) Oxygen vacancy Oxygen scavenging Dopant distribution Density of states(DoS)

#### ABSTRACT

Reducing source-drain resistance ( $R_{SD}$ ) in oxide semiconductor thin-film transistors (TFTs) mainly impacts the performance and reliability of devices and circuits. Oxygen scavenging (OS) is commonly used during process integration to reduce  $R_{SD}$ , including contact resistance between source-drain (S/D) metal and oxide semi-conductors. Meanwhile, the lower  $R_{SD}$ , the better, but the threshold voltage ( $V_T$ ) should be optimized depending on the application. Therefore, it is essential to decouple  $R_{SD}$  and  $V_T$  when applying OS.

In this study, the OS effect depending on the S/D metal of amorphous InGaZnO (a-IGZO) TFT was investigated from the perspective of decoupling  $R_{SD}$  and  $V_{T}$ . As a result of comparing Cu, Ti, and Al as S/D metals, when Al, which has a high metal–oxygen (M-O) bond strength, was used as the source-drain metal,  $V_{T}$  and  $R_{SD}$  decreased and on-current ( $I_{on}$ ) increased compared to when Ti was used. A comprehensive analysis of TFT's electrical characteristics ( $V_{T}$ , mobility,  $I_{on}$ ), X-ray photoelectron spectroscopy (XPS), subgap density of states (DoS), and lateral distribution of thermal equilibrium carrier concentration ( $n_{O}(y)$ ) indicates that the occurrence and diffusion of oxygen vacancy ( $V_{O}$ ) due to OS in the S/D region cause an increase in subgap DoS and gate-to-S/D overlap length ( $I_{OV}$ ) and a decrease in  $V_{T}$  due to an increase in donor concentration in the center of the channel ( $I_{OCH}$ ) due to a change in  $I_{OCH}$ ) profile.

While  $R_{SD}$  changes before and after post-annealing are  $\times 1.087$  (Cu),  $\times 0.606$  (Ti), and  $\times 0.283$  (Al),  $N_{CH}$  changes are  $\times 0.985$  (Cu),  $\times 1.267$  (Al), and  $\times 1.183$  (Ti). The  $\Delta V_T$ 's before and after post-annealing are + 0.119 V (Cu), -0.206 V (Al), and - 0.045 V (Ti), while  $\Delta I_{on}$ 's are  $\times 0.724$  (Cu),  $\times 1.222$  (Al), and  $\times 1.193$  (Ti). Therefore, it is found that Ti is more advantageous than Al in terms of decoupling  $R_{SD}$  and  $V_T$ .

Our result becomes more critical in employing oxide semiconductor TFTs as the back end of line (BEOL) devices because the phenomenon of  $V_T$  being affected in improving  $R_{SD}$  using OS can become more severe in high-temperature processes. Furthermore, our result suggests that when selecting S/D metals and annealing conditions for OS, it is necessary to fully consider not only the  $R_{SD}$  reduction but also the degree to which  $R_{SD}$  and  $V_T$  can be decoupled.

#### 1. Introduction

Amorphous oxide semiconductor (AOS) thin-film transistor (TFT) has a high mobility (>10 cm<sup>2</sup>/Vs) due to overlapping of metal s-orbitals, negligible gate-induced drain leakage (GIDL) due to few electron-hole pairs generated, ultra-low off-current ( $<10^{-20}$  A/ $\mu$ m) due to wide

bandgap, and CMOS back end of line (BEOL) compatibility. Recently, research on AOS TFTs has been conducted not only in displays but also in memory applications [1–6]. Therefore, increasing the integration density of AOS TFTs and reducing the source-drain (S/D) parasitic series resistance (R<sub>SD</sub>), including contact resistance, is essential. Meanwhile, in amorphous InGaZnO (a-IGZO) as a representative AOS material, oxygen

https://doi.org/10.1016/j.sse.2025.109202

<sup>&</sup>lt;sup>a</sup> School of Electrical Engineering, Kookmin University, 77 Jeongneung-ro, Seongbuk-gu, Seoul 02707, South Korea

b Department of Advanced Technology, DGIST, Daegu 42988, Korea

<sup>\*</sup> This article is part of a special issue entitled: 'KCS 2024' published in Solid State Electronics.

<sup>\*</sup> Corresponding author.

E-mail address: drlife@kookmin.ac.kr (D.H. Kim).

<sup>&</sup>lt;sup>1</sup> These authors contributed equally to this work.

vacancy ( $V_O$ ) and hydrogen (H) act as electron donors to determine key device parameters such as threshold voltage ( $V_T$ ), subthreshold swing (SS), field-effect mobility ( $\mu_{FE}$ ), on current ( $I_{on}$ ), and bias temperature instability.

To control the TFT  $V_T$  in a positive direction and optimize circuit operation, one must reduce the number of  $V_{OS}$ . However, unlike Si, as  $V_T$  increases in IGZO,  $I_{on}$  decreases exponentially, and a positive bias temperature instability (PBTI) worsens [6,7]. Therefore,  $V_T$  control and  $I_{on}$  control require an independent approach from  $R_{SD}$  control, and for this, it is essential to accurately understand the  $V_O$  concentration, which determines the carrier concentration.

Reducing  $R_{SD}$  and maintaining the target  $V_T$  is essential to achieve high  $I_{\rm on}.$  For this purpose, the carrier concentration should be locally increased in the S/D region to form an excellent ohmic contact. Additionally, as the TFT channel gets shorter, a total channel resistance  $(R_{TOT})$  is more affected by  $R_{SD}$  than carrier concentration in the channel center region [8]. Therefore, methods such as plasma treatment [9], H diffusion [10], and oxygen scavenging (OS) [1] have been widely used to increase the carrier concentration in the S/D region locally and to reduce  $R_{SD}.$

From the OS viewpoint, when the metal for the S/D electrode has a stronger metal-oxygen (M-O) bond strength than  $In_2O_3$  (346 kJ/mol),  $Ga_2O_3$  (374 kJ/mol), or ZnO (284 kJ/mol), oxygen is actively removed

from the AOS active material, forming  $V_O$  in S/D region and reducing  $R_{SD}$  [11–13]. Therefore, research is underway to implement an OS layer designed to absorb oxygen from the AOS layer. In addition, the OS effect may occur more due to thermal energy. In the case of the memory process carried out in a high-temperature process, it is necessary to determine the S/D metal and thermal budget considering the OS effect [14].

Lower  $R_{SD}$  is better, but  $V_T$  should be optimized depending on the application. Therefore, decoupling  $R_{SD}$  and  $V_T$  when applying OS is very important. Therefore, although it is necessary to analyze how the subgap density of states (DoS) and lateral distribution of thermal equilibrium carrier concentration  $(n_0(y))$  of a-IGZO active layer are affected during the OS process, previous studies have rarely verified the effect of S/D metal or annealing on DoS and  $n_0(y)$  during OS. In fact, the lateral spread of  $V_O$  during the OS changes the DoS,  $n_0(y)$ , donor concentration in the center of the channel  $(N_{CH})$ , the effective length of the gate-to- $n^+$  S/D overlap region  $(L_{OV})$ , and effective channel length  $(L_{eff})$ , and the amount of these changes means the degree to which  $V_T$  and  $R_{SD}$  can be decoupled.

In this study, the OS effect depending on the S/D metal of a-IGZO TFTs is investigated from the perspective of decoupling  $R_{\rm SD}$  and  $V_{\rm T}$ . The metals used were Cu, Ti, and Al, and the effect of post-annealing was also investigated. It was observed through X-ray photoelectron spectroscopy

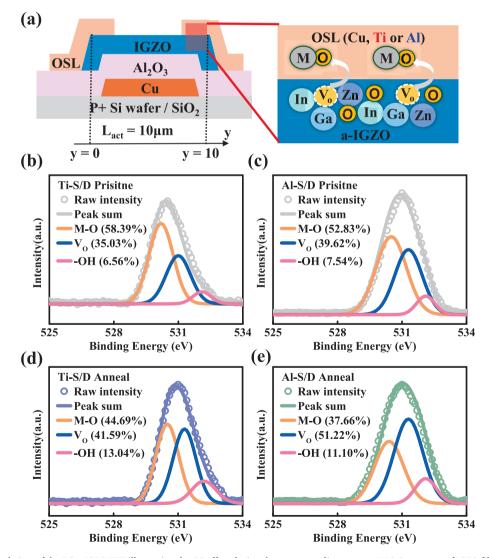

**Fig. 1.** (a) Cross-sectional view of the BG a-IGZO TFT illustrating the OS effect during the post-annealing process. XPS O<sub>1s</sub> spectra of IGZO films in the pristine (before annealing) (b) Ti-S/D and (c) Al-S/D devices. XPS O<sub>1s</sub> spectra of IGZO films after post-annealing in (d) Ti-S/D and (e) Al-S/D devices.

(XPS) that the degree to which the metal absorbs oxygen from IGZO in the S/D region varies depending on the type of S/D metal with different M-O bond strength. Furthermore, the influence of OS on the channel region as well as the S/D region was observed through the experimentally extracted subgap DoS and  $n_0(y)$  profile to compare and analyze the degree to which  $R_{SD}$  and  $V_T$  can be decoupled depending on the metal.

#### 2. Device fabrication

The fabricated a-IGZO TFT device has a staggered bottom-gate (BG) structure, as shown in Fig. 1a. The fabrication process is as follows. First, the 300-nm-thick SiO2 buffer layer was deposited by plasma-enhanced chemical vapor deposition (PECVD) on the  $p^+$ -Si substrate. Then, the 20-nm-thick Cu was deposited and patterned as a BG electrode by the ebeam evaporation and lift-off process. Subsequently, the 40-nm-thick Al<sub>2</sub>O<sub>3</sub> as a gate insulator (GI) was deposited at a low temperature of 80 °C using atomic layer deposition (ALD) with Al(CH<sub>3</sub>)<sub>3</sub> (trimethylaluminum; TMA) and H<sub>2</sub>O as a precursor. Subsequently, the 35-nm-thick a-IGZO (In:Ga:Zn = 1:1:1) was sputter-deposited at room temperature with 150 W RF power, a gas flow of Ar:O2 = 3:0.1 sccm, and pressure of 5 mTorr, and was patterned as the TFT active layer. The 40-nm-thick S/ D metal was then deposited and patterned as a S/D electrode by the ebeam evaporation and lift-off. Finally, the fabricated device was postannealed at 100 °C for 30 min in an air atmosphere. Three cases of S/ D metal were compared: Cu, Ti, and Al, and both before and after postannealing were compared.

The channel length (L) was 5  $\mu$ m and 10  $\mu$ m, and the channel width (W) was 5  $\mu$ m, 10  $\mu$ m, 50  $\mu$ m, and 100  $\mu$ m. All I-V and C-V curves were measured with an HP4156C semiconductor parameter analyzer and an HP4284A LCR meter using an alternating current signal at 60 kHz.

#### 3. Results and discussion

Fig. 1a shows a schematic view illustrating OS that occurs between IGZO and S/D metal during post-annealing. When considering the cation-oxygen binding energy or M–O binding energy at the interface between IGZO and electrode, more oxygen is absorbed from IGZO. A more significant number of  $V_{\rm OS}$  is formed at the interface between S/D metal and IGZO in the case that the M–O bond is more robust than  $\rm In_2O_3$  (346 kJ/mol), ZnO (284 kJ/mol), and  $\rm Ga_2O_3$  (374 kJ/mol). Therefore, OS metals with different M–O bond strengths, i.e., Cu (284 kJ/mol), Ti (672 kJ/mol), and Al (791 kJ/mol) [15,16], were used as the S/D electrodes

Subsequently, this study examined the IGZO layer via XPS, as shown in Fig. 1b—e. The measured distribution of the O 1 s (O $_{1s}$ ) peak obtained from the XPS analysis was decomposed into three bonding types: stoichiometric M—O, non-stoichiometric V $_{O}$ , and non-lattice—OH. The M—O peak located at 530 eV is due to the O $^{2-}$  ion of the M—O bonding in a-IGZO film. While the peak at 531.5 eV reflects V $_{O}$ s, the peak at 532.4 eV corresponds to the presence of oxygen species weakly bound to the film surface, such as –OH [17,18]. The effect of post-annealing on the atomic percent of XPS O $_{1s}$  spectra of IGZO films depending on S/D metal is summarized in Table 1.

As shown in Fig. 1b and c, the OS occurs more and the  $V_O$  peak is the highest in Al-S/D (791 kJ/mol) device, which has a stronger M-O bond than Ti-S/D (672 kJ/mol) [15,16]. When compared before and after annealing, more OS was generated through thermal energy, and in the

Table 1 Effect of post-annealing on the atomic percent of XPS  $O_{1s}$  spectra of IGZO films depending on S/D metal.

| O-content      | Ti pristine | Ti anneal | Al pristine | Al anneal |

|----------------|-------------|-----------|-------------|-----------|

| M-O            | 58.39       | 44.69     | 52.83       | 37.66     |

| V <sub>O</sub> | 35.03       | 41.59     | 39.62       | 51.22     |

| -OH            | 6.56        | 13.04     | 7.54        | 11.10     |

Al-S/D device, OS occurred the most and showed the most significant increase in  $V_O$  peak, compared to Ti-S/D device [Fig. 1d and e]. Table 1 indicates that the rise of atomic  $V_O$  percent is  $\times 1.187$  in Ti-S/D device and  $\times 1.293$  in Al-S/D device, respectively.

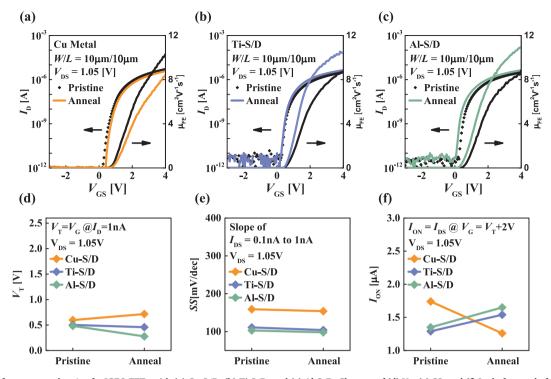

Fig. 2a–c show the transfer curves and  $\mu_{FE}$ 's before and after annealing according to S/D metal. Changes in electrical characteristics originate from  $V_O$  generated as OS occurred, consistent with XPS data. In addition,  $V_T$ , SS, and  $I_{on}$  changes before and after post-annealing according to S/D metal were shown in Fig. 2d–f, where  $V_T$  was extracted as  $V_T=V_{GS}$  at  $I_D=(W/L)\times 1nA$  at  $V_{DS}=1.05$  V. When looking at the change in  $V_T$  before and after annealing,  $V_T$  increased in the Cu-S/D device ( $\Delta V_T=+0.119$  V). This is because the M–O bond strength of Cu is weaker than that of  $In_2O_3$  (346 kJ/mol),  $Ga_2O_3$  (374 kJ/mol), and ZnO (284 kJ /mol), making it difficult for OS to occur and  $V_O$  being passivated by interdiffusion of oxygen during air annealing.

On the other hand,  $V_T$  decreased in Ti-S/D devices and Al-S/D devices, and  $V_T$  decreased the most in Al-S/D devices ( $\Delta V_T$ : Ti =-0.045 V, Al =-0.206 V). This is because OS occurred the most in Al-S/D devices with the strongest M–O bond [14,15], and  $V_O$  was generated the most. Therefore, as OS occurred, the number of  $V_O$ s, which acts as an electron donor, increased, causing an increase in carrier concentration and a decrease in  $V_T$ . After annealing, the  $I_{on}$  also increased the most in Al-S/D devices (the change in  $I_{on}$  ( $\Delta I_{on}$ ):  $\times 0.724$  (Cu),  $\times 1.222$  (Al), and  $\times 1.193$  (Ti)), where  $I_{on} = I_D$  at  $V_{GS} = V_T + 2$  V and  $V_{DS} = 1.05$  V. The  $\Delta I_{on}$  during post-annealing tends to coincide with the  $R_{SD}$  change explained in Fig. 3.

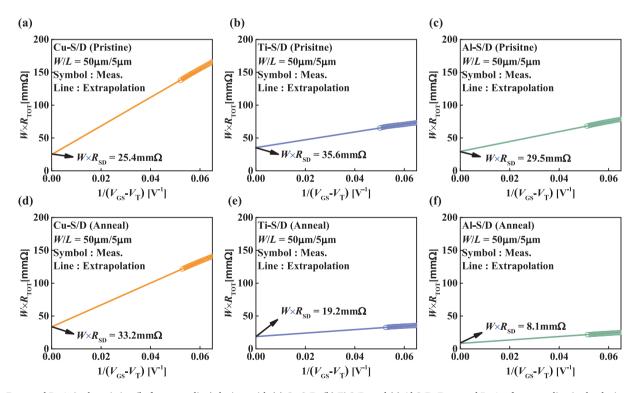

Fig. 3a and b show the change of  $R_{SD}$ , which is extracted by using the channel resistance method [19], before and after annealing according to S/D metal.  $R_{SD}$  changes after annealing were Cu (×1.087), Ti (×0.606), and Al (×0.283). In the Cu-S/D device,  $R_{SD}$  increases because the interdiffusion of oxygen passivates  $V_{O}$  during annealing, and the carrier concentration decreases. In the Ti-S/D device and Al-S/D device,  $R_{SD}$  decreased, and the greatest decrease occurred in Al-S/D devices with the strongest M–O bond strength. When OS occurs, the  $n^+$  region is formed in S/D due to oxygen deficiency of IGZO, lowering  $R_{SD}$ , which is consistent with previous studies [8,13]. OS generates  $V_{OS}$ , forming an  $n^+$  region in the S/D region, thereby reducing the thickness of the Schottky barrier. Therefore, electrons easily tunnel through the thin Schottky barrier and act like an ohmic contact [20].

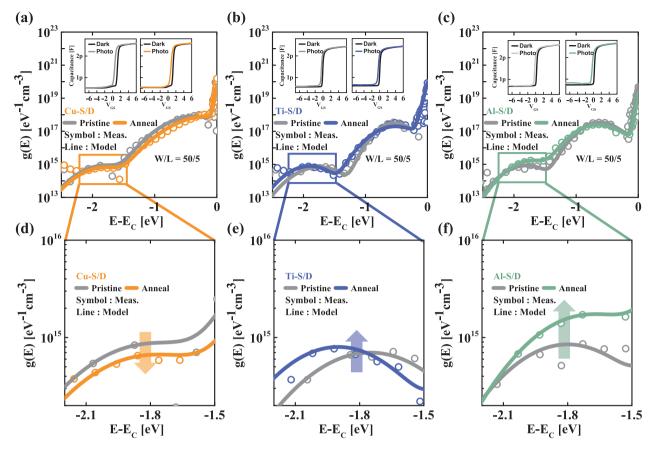

Subgap DoS determines device characteristics such as  $V_T$ , SS,  $\mu_{FE}$ ,  $I_{On}$ , and bias stress-induced instability in a-IGZO active film. In Fig. 4a–f, the change of subgap DoS of a-IGZO active film during OS was extracted using the monochromatic photonic capacitance–voltage (MPCV) technique [21,22]. This method was described in detail in our previous works [21–26], and in our case, a 7mW laser source with a wavelength of 2.8 eV optical energy was used. The measured C-V characteristics are shown in the insets of Fig. 4a–c. The  $V_O$ -related peaks in the extracted DoS are enlarged in Fig. 4d–f.

Extracted DoS can be modeled as g(E), which consists of the  $V_O$  defect state ( $g_{Vo}$ ), acceptor-like deep states ( $g_{DA}$ ), and acceptor-like tail state ( $g_{TA}$ ). Furthermore, the DoS model parameters are summarized in Table 2.

$$\begin{split} g(E) &= g_{V_O}(E) + g_{DA}(E) + g_{TA}(E) \\ &= N_{V_O} \times exp\left(-\left(\frac{E_V + E_{V_O} - E}{kT_{V_O}}\right)^2\right) + N_{DA} \\ &\times exp\left(-\left(\frac{E_C - E_{DA} - E}{kT_{DA}}\right)^2\right) + N_{TA} \times exp\left(-\frac{E_C - E}{kT_{TA}}\right) \end{split} \tag{1}$$

As shown in Fig. 4a, the  $V_O$  peak, which acts as an electron donor, decreased in Cu, and this is due to the interdiffusion of oxygen in the air during the annealing process. Fig. 4b and c indicate that the  $V_O$  peak increased in Ti and Al. This is because the  $V_O$ s created in the S/D region by OS diffuse into the channel, and the most prominent change of  $N_{V_O}$  ( $\Delta N_{V_O}$ ) (= 8.5  $\times 10^{14}$ ) was shown in the Al-S/D device, where  $V_O$  is

Fig. 2. (a) Transfer curves and  $\mu_{FE}$ 's of a-IGZO TFTs with (a) Cu-S/D, (b) Ti-S/D, and (c) Al-S/D. Changes of (d)  $V_T$ , (e) SS, and (f)  $I_{on}$  before and after post-annealing according to S/D metal.

Fig. 3. Extracted R<sub>SD</sub>'s in the pristine (before annealing) devices with (a) Cu-S/D, (b) Ti-S/D, and (c) Al-S/D. Extracted R<sub>SD</sub>'s after annealing in the devices with (d) Cu-S/D, (e) Ti-S/D, and (f) Al-S/D.

formed the most due to the strongest M-O bond.

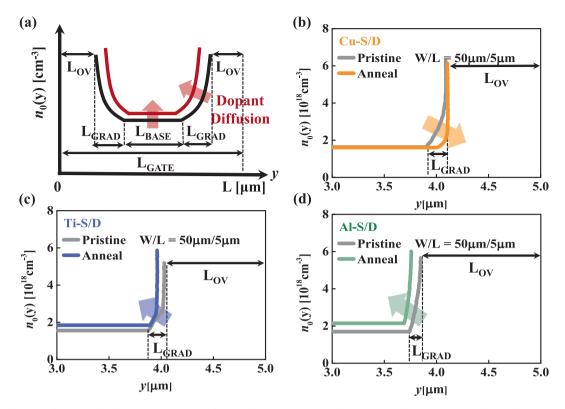

To examine the OS effects on  $N_{CH}$ ,  $L_{OV}$ , and  $L_{eff}$ , the  $n_0(y)$  profile was extracted according to S/D metal and post-annealing through C-V technique [22,27]. The change of  $n_0(y)$  during the annealing for OS is illustrated in Fig. 5a, where y is the position coordinate along the lateral channel length direction. The  $V_{OS}$  generated by OS in the S/D region can

diffuse into the channel, increasing  $N_{CH}$  and  $L_{OV}$  and decreasing  $L_{eff}$  [27]. Because in Fig. 5a, the  $n_0(y=L_{BASE}),$  i.e.,  $N_{CH},$  and  $n_0(y=L_{GRAD})$  determine  $V_T$  and  $R_{SD}$  respectively, the observation of  $n_0(y)$  during OS is essential to speculate the decoupling between  $V_T$  and  $R_{SD}$  and the control of short channel effect (SCE).

The  $n_0(y)$  profiles extracted at  $V_{GS}=0\ V$  according to S/D metal are

Fig. 4. The changes of subgap DoS before and after post-annealing in the TFT devices with (a) Cu-S/D, (b) Ti-S/D, and (c) Al-S/D. The insets show the measured C-V characteristics. The V<sub>O</sub>-related peaks in the extracted DoS are enlarged in the TFT devices with (d) Cu-S/D, (e) Ti-S/D, and (f) Al-S/D.

**Table 2**Subgap DoS parameters depending on S/D metal and before/after post-anneal conditions.

| Parameter                                                      | Cu       |        | Ti       |        | Al       |        |

|----------------------------------------------------------------|----------|--------|----------|--------|----------|--------|

|                                                                | pristine | anneal | pristine | anneal | pristine | anneal |

| $N_{V_o}(\times 10^{15})$ [cm <sup>-3</sup> eV <sup>-1</sup> ] | 0.85     | 0.65   | 0.7      | 0.8    | 0.85     | 1.7    |

| $kT_{V_o}[eV]$                                                 | 0.4      | 0.4    | 0.38     | 0.35   | 0.35     | 0.35   |

| $E_{V_o}[eV]$                                                  | 1.2      | 1.2    | 1.25     | 1.1    | 1.2      | 1.3    |

| $N_{DA}(\times 10^{17})$ [cm <sup>-3</sup> eV <sup>-1</sup> ]  | 8        | 8      | 3.2      | 3      | 3.4      | 2.5    |

| $kT_{DA}[eV]$                                                  | 0.45     | 0.5    | 0.29     | 0.35   | 0.31     | 0.35   |

| $E_{DA}[eV]$                                                   | 0.35     | 0.15   | 0.51     | 0.45   | 0.62     | 0.65   |

| $N_{TA}(\times 10^{19})$ [cm <sup>-3</sup> eV <sup>-1</sup> ]  | 6        | 6      | 9        | 9      | 6        | 2      |

| $kT_{TA}[eV]$                                                  | 0.02     | 0.02   | 0.03     | 0.03   | 0.02     | 0.02   |

shown in Fig. 5b–d. After annealing, the  $n_0(y)$  appears as dopant diffusion, as seen in Fig. 5a. When comparing the  $n_0(y)$  before annealing, it is found that the  $L_{OV}$  becomes longer in the order of Al > Ti > Cu, as shown in Fig. 5b–d. This is because the stronger the M-O bond, the more  $V_O$  is formed due to OS in the S/D area during the process, and the larger the  $V_O$  concentration, the more  $V_O$  diffusion into the channel increases  $N_{CH}$  [28].

For Cu-S/D devices,  $N_{CH}$  and  $L_{OV}$  decreased after annealing, as shown in Fig. 5b. This is because the M-O bond strength is weak, OS does not occur easily, and oxygen interdiffusion occurs during air annealing. When oxygen enters the channel, it passivates  $V_{OS}$  and lowers  $N_{CH}$ . On the other hand, as shown in Fig. 5c and d,  $N_{CH}$  and  $L_{OV}$  increased during post-annealing in Ti-S/D and Al-S/D devices.  $N_{CH}$  changes during post-annealing are  $\times 0.985$  (Cu),  $\times 1.267$  (Al), and  $\times 1.183$  (Ti). This is

because, in Ti-S/D and Al-S/D devices,  $V_O$  is formed due to OS in the S/D region, acts as a donor, creates an  $n^+$  region, and diffuses into the channel. Since the more significant the  $V_O$  concentration, the better the diffusion, the  $L_{OV}$  can increase the most in Al-S/D devices [28]. As  $N_{CH}$  increases,  $V_T$  decreases, and the extracted  $n_O(y)$  profile also matches the  $V_T$  change after annealing, as seen in Fig. 2d.

While OS occurs, one can expect only  $R_{SD}$  to get lower. However, undoubtedly, in Fig. 5b–d, it cannot be avoided that  $n_0(y)$  and subgap DoS change together as  $V_O$  diffuses into the channel. As more OS occurs,  $N_{CH}$  increases,  $V_T$  decreases,  $L_{OV}$  increases, and  $L_{eff}$  decreases.

Although it was not possible to completely decouple  $V_T$  and  $R_{SD}$ , it can be seen that Ti is more advantageous than Al from a decoupling perspective. Therefore, when selecting an S/D metal, lowering the  $R_{SD}$  as much as possible while maintaining the target  $V_T$  can be more vital in choosing the S/D metal and the annealing condition than employing simply a metal with high M–O bond strength.

# 4. Conclusion

As AOS TFTs are being researched not only in the displays but also in the memory field, the integration density of AOS TFTs needs to increase, and  $R_{SD}$  should be reduced accordingly. OS is one of the valuable methods for lowering  $R_{SD}$  in the process integration. Since OS occurs more actively in high-temperature processes, much research is also needed regarding the high-temperature stability of AOS TFTs used in CMOS BEOL.

In our work, depending on the type of S/D metal of a-IGZO TFTs, the degree to which the metal absorbs oxygen from IGZO active film in the S/D region and the degree of OS were confirmed through  $O_{1s}$  spectra of XPS. In addition, we extracted and compared  $R_{SD}$  depending on S/D metal and before/after post-annealing.

Fig. 5. (a) The schematic illustrating the change of  $n_0(y)$  during the annealing for OS. Extracted  $n_0(y)$  profiles before/after annealing in the TFT devices with (b) Cu-S/D, (c) Ti-S/D, and (d) Al-S/D.

Through subgap DoS, we verified the impact of OS occurring in the S/D region on subgap DoS in the channel area and the quantitative change in  $V_{\rm OS}$ . Moreover, changes in  $N_{\rm CH}$  and  $L_{\rm OV}$  due to diffusion of  $V_{\rm O}$  generated in S/D were observed through  $n_0(y)$  profiling. Metals with stronger M–O bonds absorbed oxygen better from IGZO, showing the most significant decrease in  $R_{\rm SD}$  and the largest increase in  $V_{\rm OS}$ . Furthermore, the more OS occurs, the higher  $N_{\rm CH}$  is due to the diffusion of  $V_{\rm O}$  formed in the S/D area. As a result,  $V_{\rm T}$  decreases,  $L_{\rm OV}$  increases, and  $L_{\rm eff}$  decreases as more OS occurs.

Therefore, OS has a trade-off relationship in that it lowers  $R_{SD}$  but reduces  $V_T$  and  $L_{\rm eff}.$  It was confirmed that Ti is more advantageous than Al in terms of  $V_T$  and  $R_{SD}$  decoupling, although  $R_{SD}$  is lower in Al-S/D devices than in Ti-S/D devices. Our approach and results can be helpful in the process and device optimization of AOS TFT devices from the perspective of  $V_T$  and  $R_{SD}$  decoupling and SCE control.

# CRediT authorship contribution statement

Seungki Kim: Data curation, Validation, Conceptualization, Formal analysis, Investigation. Wonjung Kim: Investigation, Data curation, Validation, Conceptualization, Formal analysis. Seong Hoon Jeon: Investigation, Formal analysis, Validation. Changwook Kim: Supervision. Dong Myong Kim: Supervision. Sung-Jin Choi: Supervision. Yoon Jung Lee: Supervision. Dae Hwan Kim: Supervision.

## Declaration of competing interest

The authors declare that they have no known competing financial interests or personal relationships that could have appeared to influence the work reported in this paper.

# Acknowledgements

This work was supported in part by the National Research

Foundation of Korea (NRF) funded by the Korean Government (MSIT) under Grant RS-2023-00208661, in part by the Tech Incubator Program for Startup (TIPS) funded by the Korea government under Grant 00321794 and in part by the 2023 research fund of Kookmin University in Korea. The EDA tool was supported by the IC Design Education Center (IDEC), Korea.

## References

- [1] Belmonte A, Oh H, Rassoul N, Donadio GL, Mitard J, Dekkers H, et al. Capacitor-less, long-retention (>400s) DRAM cell paving the way towards low-power and high-density monolithic 3D DRAM. Tech. Dig. Int. Electron Devices Meet. IEDM, vol. 2020- December, Institute of Electrical and Electronics Engineers Inc.; 2020, p. 28.2.1-28.2.4. https://doi.org/10.1109/IEDM13553.2020.9371900.

- [2] Belmonte A, Oh H, Subhechha S, Rassoul N, Hody H, Dekkers H, et al. Tailoring IGZO-TFT architecture for capacitorless DRAM, demonstrating > 10<sup>3</sup>s retention, >10<sup>11</sup>cycles endurance and Lg scalability down to 14nm. Tech. Dig. Int. Electron Devices Meet. IEDM, vol. 2021- December, Institute of Electrical and Electronics Engineers Inc.; 2021, p. 10.6.1-10.6.4. https://doi.org.

- [3] Duan X, Huang K, Feng J, Sun Y, Lu C, Chen C, et al. Vertical Channel-All-around (CAA) IGZO FET under 50 nm CD with High Read current of 32.8 a/m (V<sub>th</sub>+ 1 V), Well-performed thermal Stability up to 120 for Low Latency, High-density 2TOC 3D DRAM Application. Dig Tech Pap - Symp VLSI Technol 2022. https://doi.org/ 10.1109/VLSITechnologyandCir46769.2022.9830271.

- [4] Chen C, Duan X, Yang G, Lu C, Geng D, Li L, et al. Inter-Layer Dielectric Engineering for Monolithic Stacking 4F2-2 TOC DRAM with Channel-All-Around (CAA) IGZO FET to Achieve Good Reliability (>10<sup>4</sup>s Bias Stress, >10<sup>12</sup>Cycles Endurance). Tech. Dig. - Int. Electron Devices Meet. IEDM, vol. 2022- December, Institute of Electrical and Electronics Engineers Inc.; 2022, p. 2651–4.

- [5] Lu W, Zhu Z, Chen K, Liu M, Kang BM, Duan X, et al. First Demonstration of Dual-Gate IGZO 2TOC DRAM with Novel Read Operation, One Bit Line in Single Cell, I<sub>ON</sub>=1500 μA/μm@V<sub>DS</sub>=1V and Retention Time>300s. Tech. Dig. Int. Electron Devices Meet. IEDM, vol. 2022- December, Institute of Electrical and Electronics Engineers Inc.; 2022, p. 2641–4. https://doi.org/10.1109/.

- [6] Ha D, Lee W, Cho MH, Terai M, Yoo SW, Kim H, et al. Highly Manufacturable, Cost-Effective, and Monolithically Stackable 4F2 Single-Gated IGZO Vertical Channel Transistor (VCT) for sub-10nm DRAM. Tech Dig - Int Electron Devices Meet IEDM, Institute of Electrical and Electronics Engineers Inc 2023. https://doi.org/ 10.1109/IEDM45741.2023.10413772.

- [7] Kim W, Kim J, Ko D, Cha JH, Park G, Ahn Y, et al. Demonstration of crystalline IGZO transistor with high thermal stability for memory applications. Dig Tech Pap -

- Symp VLSI Technol 2023. https://doi.org/10.23919/VLSITechnologyandCir5793

- [8] Tang H, Dekkers H, Rassoul N, Sutar S, Subhechha S, Afanas Ev V., et al. Study of Contact Resistance Components in Short-Channel Indium-Gallium-Zinc-Oxide Transistor. IEEE Trans Electron Devices 2024;71:567–73. https://doi.org/ 10.1109/TED.2023.3332057.

- [9] Park JC, Lee HN, Im S. Self-Aligned Top-Gate Amorphous Indium Zinc Oxide Thin-Film Transistors Exceeding Low-Temperature Poly-Si Transistor Performance. ACS Appl Mater Interfaces 2013:247–50.

- [10] Shi Y, Tsuji M, Cho H, Ueda S, Kim J, Hosono H. Approach to Low Contact Resistance Formation on buried Interface in Oxide Thin-Film Transistors: utilization of Palladium-Mediated Hydrogen Pathway. ACS Nano 2024;18: 9736–45. https://doi.org/10.1021/acsnano.4c02101.

- [11] Kim MS, Jung S, Hyukahn J, Kim HT, Kim HJ. Enhanced Electrical Characteristics of Low-Temperature Processed In-Ga-Zn-0 Thin-Film Transistors with Oxygen Scavenging Layer. Dig. Tech. Pap. - SID Int. Symp., vol. 53, John Wiley and Sons Inc; 2022, p. 145–6. https://doi.org/10.1002/sdtp.15438.

- [12] van Setten MJ, Dekkers HFW, Kljucar L, Mitard J, Pashartis C, Subhechha S, et al. Oxygen defect Stability in Amorphous, C-Axis Aligned, and Spinel IGZO. ACS Appl Electron Mater 2021;3:4037–46. https://doi.org/10.1021/acsaelm.1c00553.

- [13] Subhechha S, Rassoul N, Belmonte A, Delhougne R, Banerjee K, Donadio GL, et al. First demonstration of sub-12 nm Lg gate last IGZO-TFTs with oxygen tunnel architecture for front gate devices. Dig Tech Pap - Symp VLSI Technol 2021.

- [14] Ritzenthaler R, Schram T, Spessot A, Caillat C, Na HJ, Lee SG, et al. Thermal budget impact on HKMG Al<sub>2</sub>O<sub>3</sub> and La gate stacks for advanced DRAM periphery transistors. IEEE Work Microelectron Electron Devices, WMED 2014:2. https://doi. org/10.1109/WMED.2014.6818721.

- [15] Yoon CS, Kim HT, Kim MS, Yoo H, Park JW, Choi DH, et al. Vertically Graded Oxygen Deficiency for improving Electrical Characteristics and Stability of Indium Gallium Zinc Oxide Thin-Film Transistors. ACS Appl Mater Interfaces 2021;13: 4110–6. https://doi.org/10.1021/acsami.0c15017.

- [16] Hsu HH, Chang CY, Cheng CH, Chiou SH, Huang CH. High mobility bilayer metaloxide thin film transistors using titanium-doped InGaZnO. IEEE Electron Device Lett 2014;35:87–9. https://doi.org/10.1109/LED.2013.2290707.

- [17] Yao J, Xu N, Deng S, Chen J, She J, Shieh HPD, et al. Electrical and photosensitive characteristics of a-IGZO TFTs related to oxygen vacancy. IEEE Trans Electron Devices 2011;58:1121–6. https://doi.org/10.1109/TED.2011.2105879.

- [18] Choi S, Kim JY, Kang H, Ko D, Rhee J, Choi SJ, et al. Effect of oxygen content on current stress-induced instability in bottom-gate amorphous InGaZnO thin-film

- transistors. Materials (Basel) 2019;12:3149. https://doi.org/10.3390/ma12193149

- [19] De La Moneda FH, Kotecha HN, Shatzkes M. Measurement of MOSFET constants. IEEE Electron Device Lett 1982;3:10–2. https://doi.org/10.1109/EDL.1982.25456.

- [20] Yun PS, Koike J. Metal Reaction Doping and Ohmic Contact with Cu-Mn Electrode on Amorphous In-Ga-Zn-O Semiconductor. J Electrochem Soc 2011;158:H1034. https://doi.org/10.1149/1.3621723.

- [21] Choi S, Park J, Hwang SH, Kim C, Kim YS, Oh S, et al. Excessive Oxygen Peroxide Model-Based Analysis of Positive-Bias-Stress and Negative-Bias-Illumination-Stress Instabilities in Self-Aligned Top-Gate Coplanar In–Ga–Zn–O Thin-Film Transistors. Adv Electron Mater 2022;8:5. https://doi.org/10.1002/aelm.202101062.

- [22] Yang TJ, Kim JH, Ryoo CII, Myoung SJ, Kim C, Baeck JH, et al. Analysis of Drain-Induced Barrier Lowering in InGaZnO Thin-Film Transistors. IEEE Trans Electron Devices 2023;70:121–6. https://doi.org/10.1109/TED.2022.3223642.

- [23] Jang JT, Choi SJ, Kim DM, Kim DH. The Calculation of negative Bias Illumination Stress-Induced Instability of Amorphous InGaZnO Thin-Film Transistors for Instability-Aware Design. IEEE Trans Electron Devices 2018;65:1002–8. https://doi.org/10.1109/TED.2018.2797208.

- [24] Choi S, Jang J, Kang H, Baeck JH, Bae JU, Park KS, et al. Systematic Decomposition of the positive Bias stress Instability in Self-Aligned Coplanar InGaZnO Thin-Film Transistors. IEEE Electron Device Lett 2017;38:580–3. https://doi.org/10.1109/ LED.2017.2681204.

- [25] Bae H, Choi H, Jun S, Jo C, Kim YH, Hwang JS, et al. Single-Scan monochromatic photonic capacitance-voltage technique for extraction of subgap dos over the bandgap in amorphous semiconductor tfts. IEEE Electron Device Lett 2013;34: 1524-6. https://doi.org/10.1109/LED.2013.2287511.

- [26] Park JH, Jeon K, Lee S, Kim S, Kim S, Song I, et al. Extraction of density of states in amorphous GaInZnO thin-film transistors by combining an optical charge pumping and capacitance-voltage characteristics. IEEE Electron Device Lett 2008;29: 1292–5. https://doi.org/10.1109/LED.2008.2006415.

- [27] Ryoo, C. I., Yang, T. J., Lee, H. J., Bae, J. H., Choi, S. J., Kim, et al. Thermally Activated and Field-Enhanced Diffusion of Dopants in a-InGaZnO TFTs Under Circuit Operations and Correlation to Device Stabilities. In SID Symposium Digest of Technical Papers 2022;53:1149-1152. https://doi.org/10.1002/sdtp.15705.

- [28] Myoung SJ, Il RC, Kim C, Choi SJ, Kim DM, Bae JH, et al. Thermal Process and Dopant Diffusion Model of a-InGaZnO TFTs for VTPrediction using Lateral Carrier Density Profiling Technique. IEEE Electron Device Lett 2023;44:630–3. https:// doi.org/10.1109/LED.2023.3242332.